# REASONING ABOUT SOFTWARE IN THE PRESENCE OF TRANSIENT FAULTS

FRANCES JANE PERRY

A DISSERTATION PRESENTED TO THE FACULTY OF PRINCETON UNIVERSITY IN CANDIDACY FOR THE DEGREE OF DOCTOR OF PHILOSOPHY

RECOMMENDED FOR ACCEPTANCE By the Department of Computer Science

Advisor: David P. Walker

September 2008

© Copyright by Frances Jane Perry, 2008. All rights reserved.

#### Abstract

A transient fault occurs when an energetic particle strikes a chip and causes a change in state in the processor. Although there is no permanent damage, the current computation may become corrupt. Transient faults have been shown to be the cause of crashes at major companies, and current technology trends will make future processors more susceptible to them. Researchers have already developed a number of solutions using combinations of software and hardware where the general approach is to duplicate computations and check for consistency between the copies. Unfortunately, generating correct fault-tolerant code is difficult, and there has been little research on proving the correctness of these techniques. Reasoning formally about fault tolerance is challenging, because invariants that hold at compile time, such as standard type safety, may not actually hold at runtime. Previous work on formalizing fault tolerance has been at the high level, including proofs about fault-tolerant algorithms and the definition of a fault-tolerant lambda calculus.

This dissertation presents the first set of techniques for statically proving fault-tolerance properties of actual executable code. To address this challenge, we develop modifications to the general methodology for typed assembly languages. An assembly-level type system incorporates invariants about fault tolerance that are strong enough to prove that all well-typed programs have the desired behaviors. All that is required to guarantee that a specific piece of code is fault-tolerant is to type-check the code at the conclusion of compilation.

More specifically, we introduce a family of three type systems.  $TAL_{FT}$  is a core language with simple instructions that guarantees that well-typed programs implementing a hybrid fault-tolerance scheme will always detect a single fault before the fault can affect the observable behavior of the program.  $ETAL_{FT}$  extends  $TAL_{FT}$  with features necessary to support realistic compilation, including stack activation frames and dynamic memory allocation. The third language,  $TAL_{CF}$ , precisely captures the behavior of software solutions for control flow faults and can provably detect any fault that causes incorrect control transfers between basic blocks before control exits that first incorrect block. Although each typed assembly language is designed for a specific hardware context, the type systems and proof methods use similar designs, allowing us to demonstrate general approaches needed for reasoning in the presence of transient faults. For example, to statically reason about values that may be corrupted at runtime, we generalize the "color systems" of previous work into a framework for classifying values with related reliability properties.

As well as being the first to prove that executable code is fault-tolerant, this dissertation makes three additional contributions. By including a language of static expressions within the type system, we can verify low-level fault-tolerant code independently of the compilation process. We show to apply fault-tolerant typed assembly languages to two different fault models: a hybrid system to detect data faults and a software-only system to detect control-flow faults. Finally, we investigate how to generate fault-tolerant typed assembly language for a realistic compiler.

#### Acknowledgments

This dissertation owes the most to my advisor David Walker. He is an extremely knowledgeable and patient teacher who taught me to be clear and rigorous in my work and confident in myself. I clearly remember the day I first openly disagreed with him, and he responded, "That's it! Now you are becoming a researcher."

The members of my thesis committee were extremely helpful in improving the quality of this dissertation, as well as my job talk. I am very grateful for their time and feedback. Andrew Appel helped me develop clear explanations and pull out the high-level ideas. David Tarditi inspired me to work that bit harder to become a better writer. Margaret Martonosi and David August's different backgrounds helped me target my work to the broader community.

Additionally, this dissertation benefited from the support of many others. George Reis and Neil Vachharajani were a great help with the architecture side of things. I am grateful for the wonderful administrative help and friendship of the staff at Princeton, especially Melissa Lawson and Donna O'Leary. This work was funded by the National Science Foundation award CNS-0627650 and a Microsoft fellowship. Any opinions, findings, and conclusions or recommendations expressed in this material are mine and do not necessarily reflect the views of the NSF or Microsoft.

During internships at Microsoft, I was lucky to work with a number of amazing people. Manuvir Das, Jason Yang, and the PAG group taught me that sometimes it's okay to sacrifice soundness, as long as you can find real bugs in real code. Juan Chen and Chris Hawblitzel showed me the joy of straddling the boundary between theory and practice to design elegant, yet practical, systems.

My fellow students were always there to advise me, commiserate with me, and support me. (And, of course, procrastinate with me...) Limin Jia was both a fantastic colleague and a close friend, and our afternoon tea times were always a bright spot in my day. Ananya Misra's sarcastic emails and dry wit kept me laughing. Siggi Cherem and Sharon Betz kept me sane through the home stretch. In addition, my survival of grad school is due in part to Melissa Carroll, Dan Dantas, Haakon Larson, Guilherme Ottoni, Shirley Gaw, Henning Rohde, Zach Anderson, Akash Lal, Dan Wang, Jay Liggatti, the pizza crowd, my officemates, and many others.

My family's continued love and support means everything to me. My father Jeff, though he never did teach me how to throw a ball, encouraged me through my disgruntled phases and kept me focused on the final goal; my mother Liz reminded me to take care of myself and was always willing to proofread my papers for punctuation, even if the words themselves were gobbledygook. As we grew up, my sister Julia and I realized we loved each other after all, and our differences turned out to be quite complementary – I fix her computer and she picks out my interview suits. Erik, Isabelle, Becky, Ben, and Hunter have become my second family. They were always there, kept Dan and me well-fed, and rushed to our aid during the occasional emergency. I will greatly miss having them so close by. My "Aunt" Marilyn is always proud of me and reminds me to be proud of myself.

And finally, there is Dan. Although his continual jokes about "Frances the 12th year grad student" did get a bit old, he is, and always will be, my best friend. I am thrilled to have him by my side as we enter this next phase in our lives – moving cross country, becoming homeowners, making new friends, and who knows what else!

### Contents

|   | Abst | tract   |                                   | iii |

|---|------|---------|-----------------------------------|-----|

| 1 | Intr | oductio | on and Background                 | 1   |

|   | 1.1  | Transi  | ent Faults                        | 1   |

|   |      | 1.1.1   | Issues Caused by Transient Faults | 1   |

|   |      | 1.1.2   | Transient Fault Trends            | 3   |

|   | 1.2  | Existir | ng Transient Fault Solutions      | 4   |

|   |      | 1.2.1   | An Example Solution: SWIFT        | 5   |

|   |      | 1.2.2   | Do Existing Solutions Work?       | 6   |

|   | 1.3  | Proof-  | Carrying Code                     | 7   |

|   |      | 1.3.1   | Typed Assembly Languages          | 7   |

|   |      | 1.3.2   | Using Typed Assembly Languages    | 8   |

|   | 1.4  | Thesis  | Scope                             | 10  |

|   |      | 1.4.1   | Modeling Transient Faults         | 10  |

|   |      | 1.4.2   | Defining Fault Tolerance          | 12  |

|   |      | 1.4.3   | Invariants of Fault Tolerance     | 13  |

|   |      | 1.4.4   | Proving Fault Tolerance           | 13  |

|   |      | 1.4.5   | Compiling for Fault Tolerance     | 14  |

|   | 1.5  | Thesis  | Organization                      | 14  |

#### CONTENTS

| TAL | FT : Fa                                                                                                            | ult-tolerant Typed Assembly Language                                                                                                                                                                                                                                         | 15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|-----|--------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2.1 | The Fa                                                                                                             | ult-Tolerant Hardware                                                                                                                                                                                                                                                        | 16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|     | 2.1.1                                                                                                              | The Fault Model                                                                                                                                                                                                                                                              | 18                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|     | 2.1.2                                                                                                              | Instruction Semantics                                                                                                                                                                                                                                                        | 20                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 2.2 | Typing                                                                                                             | g                                                                                                                                                                                                                                                                            | 28                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|     | 2.2.1                                                                                                              | Static Expressions                                                                                                                                                                                                                                                           | 30                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|     | 2.2.2                                                                                                              | Value Typing                                                                                                                                                                                                                                                                 | 33                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|     | 2.2.3                                                                                                              | Instruction Typing                                                                                                                                                                                                                                                           | 35                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|     | 2.2.4                                                                                                              | Machine State Typing                                                                                                                                                                                                                                                         | 44                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 2.3 | Forma                                                                                                              | l Results                                                                                                                                                                                                                                                                    | 47                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|     | 2.3.1                                                                                                              | Type Safety                                                                                                                                                                                                                                                                  | 48                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|     | 2.3.2                                                                                                              | Fault Tolerance                                                                                                                                                                                                                                                              | 49                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 2.4 | Perform                                                                                                            | mance                                                                                                                                                                                                                                                                        | 51                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 2.5 | Summ                                                                                                               | ary                                                                                                                                                                                                                                                                          | 53                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|     |                                                                                                                    |                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| ETA | $L_{FT}$ : G                                                                                                       | enerating fault-tolerant assembly code                                                                                                                                                                                                                                       | 54                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 3.1 | MiniC                                                                                                              |                                                                                                                                                                                                                                                                              | 55                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 3.2 | Extend                                                                                                             | ling TAL <sub>FT</sub> to $\text{ETAL}_{\text{FT}}$                                                                                                                                                                                                                          | 57                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

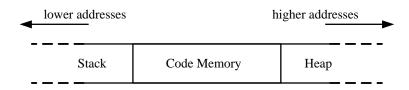

|     | 3.2.1                                                                                                              | Memory Layout                                                                                                                                                                                                                                                                | 57                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|     | 3.2.2                                                                                                              | Stacks                                                                                                                                                                                                                                                                       | 59                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|     | 3.2.3                                                                                                              | Memory Allocation and Initialization                                                                                                                                                                                                                                         | 69                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|     | 3.2.4                                                                                                              | Removal of Color Tags                                                                                                                                                                                                                                                        | 74                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|     | 3.2.5                                                                                                              | Other Changes                                                                                                                                                                                                                                                                | 76                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 3.3 | ETAL                                                                                                               | FT Formal Results                                                                                                                                                                                                                                                            | 77                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|     | 3.3.1                                                                                                              | Type Safety                                                                                                                                                                                                                                                                  | 77                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|     | <ul> <li>2.1</li> <li>2.2</li> <li>2.3</li> <li>2.4</li> <li>2.5</li> <li>ETA</li> <li>3.1</li> <li>3.2</li> </ul> | 2.1 The Fa<br>2.1.1<br>2.1.1<br>2.1.2<br>2.2 Typing<br>2.2.1<br>2.2.2<br>2.2.3<br>2.2.4<br>2.3 Forma<br>2.3.1<br>2.3.2<br>2.4 Perform<br>2.5 Summ<br>ETAL <sub>FT</sub> : G<br>3.1 MiniC<br>3.2 Extend<br>3.2.1<br>3.2.2<br>3.2.3<br>3.2.4<br>3.2.5<br>3.3 ETAL <sub>I</sub> | 2.1.1The Fault Model2.1.2Instruction Semantics2.2Typing2.2.1Static Expressions2.2.2Value Typing2.2.3Instruction Typing2.2.4Machine State Typing2.3Formal Results2.3.1Type Safety2.3.2Fault Tolerance2.4Performance2.5SummarySummaryETAL <sub>FT</sub> : Generating fault-tolerant assembly code3.1Minic3.2Extending TAL <sub>FT</sub> to ETAL <sub>FT</sub> 3.2.1Memory Layout3.2.2Stacks3.2.3Memory Allocation and Initialization3.2.4Removal of Color Tags3.3ETAL <sub>FT</sub> Formal Results |

viii

|   |     | 3.3.2                                          | Fault Tolerance                  |    |  |  |  |

|---|-----|------------------------------------------------|----------------------------------|----|--|--|--|

|   | 3.4 | 4 Translation from MiniC to ETAL <sub>FT</sub> |                                  |    |  |  |  |

|   |     | 3.4.1                                          | Translation Introduction         | 32 |  |  |  |

|   |     | 3.4.2                                          | Translation Details              | 33 |  |  |  |

|   |     | 3.4.3                                          | Translation Formal Results       | 35 |  |  |  |

|   | 3.5 | 5 Translation Example                          |                                  |    |  |  |  |

|   | 3.6 | Type-p                                         | preserving Optimizations         | 92 |  |  |  |

|   |     | 3.6.1                                          | General Considerations           | 93 |  |  |  |

|   |     | 3.6.2                                          | Removal of Redundant Moves       | 94 |  |  |  |

|   |     | 3.6.3                                          | Register Allocation              | 94 |  |  |  |

|   |     | 3.6.4                                          | Common Subexpression Elimination | 94 |  |  |  |

|   |     | 3.6.5                                          | Dead Code Elimination            | 95 |  |  |  |

|   |     | 3.6.6                                          | Constant Folding and Propagation | 95 |  |  |  |

|   |     | 3.6.7                                          | Stack Packing                    | 95 |  |  |  |

|   |     | 3.6.8                                          | Instruction Scheduling           | 96 |  |  |  |

|   | 3.7 | Summ                                           | ary                              | 97 |  |  |  |

| 4 | TAL | <sub>CF</sub> : Re                             | asoning about Control Flow 9     | )8 |  |  |  |

|   | 4.1 | Inform                                         | nal Overview                     | )0 |  |  |  |

|   | 4.2 | The Co                                         | ontrol-Flow Machine              | )6 |  |  |  |

|   |     | 4.2.1                                          | Dynamic Semantics                | )7 |  |  |  |

|   | 4.3 | Typing                                         | g                                | 1  |  |  |  |

|   |     | 4.3.1                                          | Value Typing                     | 7  |  |  |  |

|   |     | 4.3.2                                          | Instruction Typing               | 21 |  |  |  |

|   |     | 4.3.3                                          | Block Typing                     | 23 |  |  |  |

#### CONTENTS

|   |            | 4.3.4                                                                          | Machine State Typing                      | . 126                                                                                                                                             |  |  |

|---|------------|--------------------------------------------------------------------------------|-------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

|   | 4.4        | Forma                                                                          | l Results                                 | . 128                                                                                                                                             |  |  |

|   | 4.5        | Transl                                                                         | Translation                               |                                                                                                                                                   |  |  |

|   | 4.6        | Summ                                                                           | ary and Future Work                       | . 131                                                                                                                                             |  |  |

| 5 | Rela       | ted Wo                                                                         | ork and Conclusion                        | 133                                                                                                                                               |  |  |

|   | 5.1        | PCC a                                                                          | nd TAL                                    | . 133                                                                                                                                             |  |  |

|   | 5.2        | Resear                                                                         | rch in Transient Fault Tolerance          | . 135                                                                                                                                             |  |  |

|   |            | 5.2.1                                                                          | Hardware-Based Solutions                  | . 135                                                                                                                                             |  |  |

|   |            | 5.2.2                                                                          | Software-Based Solutions                  | . 136                                                                                                                                             |  |  |

|   |            | 5.2.3                                                                          | Hybrid Solutions                          | . 140                                                                                                                                             |  |  |

|   | 5.3        | Forma                                                                          | l Reasoning about Faults                  | . 140                                                                                                                                             |  |  |

|   | 5.4        | Conclu                                                                         | uding Remarks                             | . 142                                                                                                                                             |  |  |

|   |            |                                                                                |                                           |                                                                                                                                                   |  |  |

| A | TAL        | FT Proo                                                                        | of Details                                | 145                                                                                                                                               |  |  |

| A |            |                                                                                | of Details<br>as                          |                                                                                                                                                   |  |  |

| A |            |                                                                                |                                           | . 145                                                                                                                                             |  |  |

| A |            | Lemm                                                                           | as                                        | . 145<br>. 146                                                                                                                                    |  |  |

| A |            | Lemm<br>A.1.1                                                                  | as                                        | . 145<br>. 146<br>. 147                                                                                                                           |  |  |

| Α |            | Lemm<br>A.1.1<br>A.1.2                                                         | as                                        | . 145<br>. 146<br>. 147<br>. 149                                                                                                                  |  |  |

| A |            | Lemm<br>A.1.1<br>A.1.2<br>A.1.3<br>A.1.4                                       | as    Properties of Static Expressions    | . 145<br>. 146<br>. 147<br>. 149<br>. 150                                                                                                         |  |  |

| A | A.1        | Lemm<br>A.1.1<br>A.1.2<br>A.1.3<br>A.1.4<br>Type S                             | as    Properties of Static Expressions    | . 145<br>. 146<br>. 147<br>. 149<br>. 150<br>. 151                                                                                                |  |  |

| Α | A.1<br>A.2 | Lemm<br>A.1.1<br>A.1.2<br>A.1.3<br>A.1.4<br>Type S                             | as    Properties of Static Expressions    | . 145<br>. 146<br>. 147<br>. 149<br>. 150<br>. 151<br>. 154                                                                                       |  |  |

| A | A.1<br>A.2 | Lemm<br>A.1.1<br>A.1.2<br>A.1.3<br>A.1.4<br>Type S<br>Multis                   | as    Properties of Static Expressions    | . 145<br>. 146<br>. 147<br>. 149<br>. 150<br>. 151<br>. 154<br>. 154                                                                              |  |  |

| Α | A.1<br>A.2 | Lemm<br>A.1.1<br>A.1.2<br>A.1.3<br>A.1.4<br>Type S<br>Multis<br>A.3.1<br>A.3.2 | as       Properties of Static Expressions | <ul> <li>. 145</li> <li>. 146</li> <li>. 147</li> <li>. 149</li> <li>. 150</li> <li>. 151</li> <li>. 151</li> <li>. 154</li> <li>. 158</li> </ul> |  |  |

|   |       | A.4.2               | Singlestep Fault Detection       | . 160 |

|---|-------|---------------------|----------------------------------|-------|

|   |       | A.4.3               | Multistep Fault Detection        | . 161 |

|   |       | A.4.4               | Fault Similarity                 | . 163 |

|   |       | A.4.5               | Fault Tolerance Theorem          | . 164 |

| B | Min   | іС Турі             | ng Rules                         | 166   |

| С | Com   | plete R             | Rules for ETAL <sub>FT</sub>     | 169   |

|   | C.1   | Syntax              | a of Machine States              | . 169 |

|   | C.2   | Dynan               | nic Semantics                    | . 170 |

|   |       | C.2.1               | Fault Rules                      | . 170 |

|   |       | C.2.2               | Normal Execution Rules           | . 170 |

|   | C.3   | Static S            | Semantics                        | . 174 |

|   |       | C.3.1               | Syntax                           | . 174 |

|   |       | C.3.2               | Properties of Static Expressions | . 174 |

|   |       | C.3.3               | Value Typing                     | . 176 |

|   |       | C.3.4               | Subtyping                        | . 177 |

|   |       | C.3.5               | Stack Typing Judgments           | . 178 |

|   |       | C.3.6               | Instruction Typing Rules         | . 179 |

|   |       | C.3.7               | Machine State Typing             | . 183 |

|   | C.4   | Simula              | ation of Machine States          | . 185 |

|   |       | C.4.1               | Color Extraction                 | . 185 |

|   |       | C.4.2               | Simulation                       | . 186 |

| D | ETA   | L <sub>FT</sub> Foi | rmal Results                     | 188   |

|   | D.1   |                     | ied Lemmas                       |       |

|   | - • • |                     |                                  |       |

|   | D.2 | New Lemmas For Stacks                    |                                    |     |  |  |

|---|-----|------------------------------------------|------------------------------------|-----|--|--|

|   | D.3 | New Lemmas For Dynamic Memory Allocation |                                    |     |  |  |

|   | D.4 | Type Safety                              |                                    |     |  |  |

|   | D.5 | Fault To                                 | blerance                           | 195 |  |  |

|   |     |                                          |                                    |     |  |  |

| Ε | Min |                                          | AL <sub>FT</sub> Translation       | 198 |  |  |

|   | E.1 | Overvie                                  | W                                  | 198 |  |  |

|   | E.2 | Translat                                 | ting Typing Information            | 200 |  |  |

|   |     | E.2.1                                    | Type Translation                   | 200 |  |  |

|   |     | E.2.2                                    | Context Generation                 | 200 |  |  |

|   | E.3 | Extendi                                  | ng Code Memory                     | 203 |  |  |

|   |     | E.3.1                                    | Invariants Between Functions       | 204 |  |  |

|   |     | E.3.2                                    | Partial Code Memories              | 205 |  |  |

|   |     | E.3.3                                    | Invariants within a Function       | 205 |  |  |

|   |     | E.3.4                                    | Adding Instructions to Code Memory | 207 |  |  |

|   | E.4 | Value T                                  | ranslation                         | 208 |  |  |

|   | E.5 | Value L                                  | ist Translation                    | 210 |  |  |

|   | E.6 | Local D                                  | Declaration Translation            | 211 |  |  |

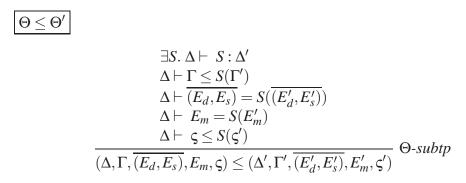

|   | E.7 | Stateme                                  | ent Translation                    | 215 |  |  |

|   | E.8 | Function Translation                     |                                    |     |  |  |

|   |     | E.8.1                                    | Prologue and Epilogue              | 216 |  |  |

|   |     | E.8.2                                    | Function Translation Judgment      | 217 |  |  |

|   | E.9 |                                          | n Translation                      |     |  |  |

|   |     | C                                        |                                    |     |  |  |

| F | TAL | CF <b>Form</b>                           | al Results                         | 221 |  |  |

|   | F.1 | Type Sa                                  | fety                               | 221 |  |  |

|                |        | F.1.1                            | Typing Lemmas                 | . 221 |  |  |

|----------------|--------|----------------------------------|-------------------------------|-------|--|--|

|                |        | F.1.2                            | Type Safety                   | . 224 |  |  |

|                | F.2    | Fault 7                          | Folerance Results             | . 226 |  |  |

|                |        | F.2.1                            | Machine State Simulation      | . 226 |  |  |

|                |        | F.2.2                            | Block Execution               | . 226 |  |  |

|                |        | F.2.3                            | Fault Recovery                | . 228 |  |  |

|                |        | F.2.4                            | Block Transitions             | . 229 |  |  |

|                |        | F.2.5                            | Program Execution             | . 230 |  |  |

|                |        | F.2.6                            | The Fault Tolerance Theorem   | . 231 |  |  |

| G              | TAL    | <sub>CF</sub> Trar               | nslation                      | 234   |  |  |

|                | G.1    | A Sim                            | ple While Loop Language       | . 234 |  |  |

|                | G.2    | Check                            | ing Code and Exit Code Macros | . 235 |  |  |

|                | G.3    | 3 Translating Variable Context V |                               |       |  |  |

|                | G.4    | 4 Partial Translations           |                               |       |  |  |

|                | G.5    | G.5 Translating Statements       |                               |       |  |  |

|                | G.6    | The Tr                           | ranslation Theorem            | . 241 |  |  |

| <b>T</b> 5 • 1 |        |                                  |                               | 0.42  |  |  |

| <b>B</b> 1     | DIIOgi | aphy                             |                               | 243   |  |  |

## **List of Figures**

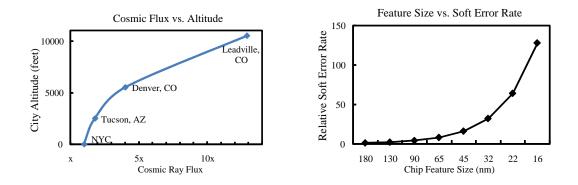

| 1.1  | Effects of Altitude [76] and Feature Size [11] on Transient Faults       | 3  |

|------|--------------------------------------------------------------------------|----|

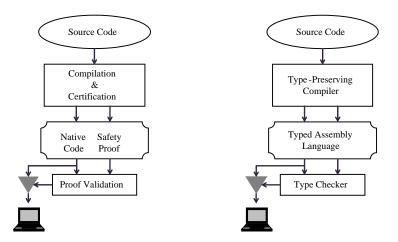

| 1.2  | Proof-Carrying Code [42] and Typed Assembly Language [39]                | 8  |

| 2.1  | Syntax of instructions and machine states.                               | 18 |

| 2.2  | Operational rules for basic instructions.                                | 21 |

| 2.3  | Selected operational rules for memory instructions                       | 23 |

| 2.4  | Operational rules for control flow instructions                          | 27 |

| 2.5  | $TAL_{FT}$ type syntax                                                   | 29 |

| 2.6  | Semantics of Static Expressions, Part 1                                  | 31 |

| 2.7  | Semantics of Static Expressions, Part 2                                  | 32 |

| 2.8  | Value Typing.                                                            | 34 |

| 2.9  | Subtyping                                                                | 36 |

| 2.10 | Instruction Typing Rules for Basic Instructions and Memory Instructions. | 39 |

| 2.11 | Instruction Typing Rules for Jump Instructions.                          | 41 |

| 2.12 | Instruction Typing Rules for Branch Instructions.                        | 42 |

| 2.13 | Machine State Element Typing                                             | 45 |

| 2.14 | Machine State Typing.                                                    | 46 |

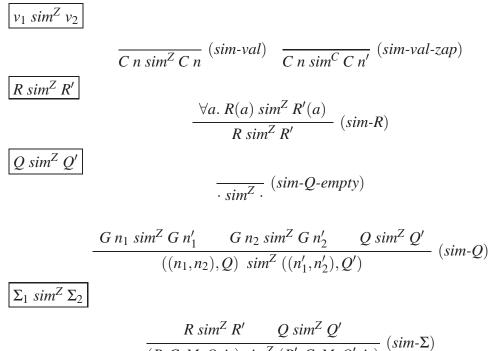

| 2.15 | Similarity of Machine States.                                            | 50 |

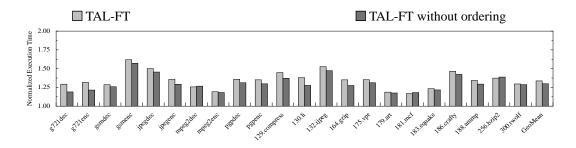

| 2.16 | Performance Normalized to Unprotected Version.                      | 51  |

|------|---------------------------------------------------------------------|-----|

| 3.1  | MiniC Example Program.                                              | 55  |

| 3.2  | MiniC Syntax.                                                       | 56  |

| 3.3  | New Instruction Syntax and Operation Semantics to Support Stacks    | 60  |

| 3.4  | Modifications to Value Typing, Subtyping, and Well-Formed Judgments | 64  |

| 3.5  | Stack Lookup and Update.                                            | 65  |

| 3.6  | Typing Rules for the New Stack Instructions.                        | 67  |

| 3.7  | Stack Typing.                                                       | 68  |

| 3.8  | New Operation Semantics to Support Dynamic Memory Allocation        | 70  |

| 3.9  | Additions to Subtyping to Support Reference Initialization          | 71  |

| 3.10 | Instruction Typing Rules to Support Dynamic Memory Allocation       | 73  |

| 3.11 | Changes to Memory Typing Judgments.                                 | 75  |

| 3.12 | Changes to the Machine State Typing Judgment.                       | 76  |

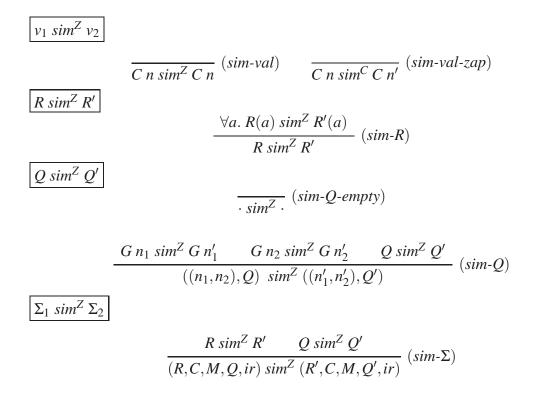

| 3.13 | Similarity of Machine States.                                       | 80  |

| 3.14 | Summary of Translation Judgments.                                   | 84  |

| 3.15 | Summary of Type Translation Judgments.                              | 85  |

| 3.16 | Example Translation from MiniC to $\text{ETAL}_{\text{FT}}$         | 87  |

| 4.1  | Machine State Syntax.                                               | 106 |

| 4.2  | Operational Semantics.                                              | 110 |

| 4.3  | Properties of colored values and zap tags.                          | 114 |

| 4.4  | Example: Protocol Stages.                                           | 115 |

| 4.5  | Typing Syntax.                                                      | 116 |

| 4.6  | Static Expression Judgments, Part 1                                 | 118 |

| 4.7  | Static Expression Judgments, Part 2                                 | 119 |

| 4.8  | Value Typing Judgment and Subtyping Judgment                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4.9  | Instruction Typing Judgment                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 4.10 | Block Typing Judgment                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 4.11 | Machine State Typing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| A.1  | Example Cases of Theorem 25 (Progress)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| A.2  | Example Case from Theorem 26 (Preservation) Part 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| A.3  | Example Case from Theorem 26 (Preservation) Part 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| A.4  | Example Case of Theorem 26 (Preservation) Part 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| A.5  | Similarity of Machine States                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| A.6  | Example Case of Lemma 30                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| E.1  | Type Translation.         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         .         . |

| E.2  | Statement Translation - Basic Statements                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| E.3  | While Statement Translation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| E.4  | If Statement Translation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| E.5  | Function Call Translation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| G.1  | Translation of While Programs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

### **Chapter 1**

### **Introduction and Background**

#### **1.1 Transient Faults**

A *transient fault* occurs when an energetic particle strikes a transistor or wire in a processor and causes a change in state. These particles do not permanently damage the hardware, but they may corrupt the computation that is currently executing by depositing a charge that alters stored values and signals.

#### **1.1.1 Issues Caused by Transient Faults**

As one might expect, transient faults can cause a host of issues. In particular, as these anecdotes show, systems can crash due to transient faults.

• In 2000, Sun Microsystems acknowledged that transient faults interfered with cache memories and caused crashes in server systems at major customer sites, including AOL, eBay, and dozens of others [6].

- Cypress Semiconductor has stated "The wake-up call came in the end of 2001 with a major customer reporting havoc at a large telephone company. Technically it was found that a single soft fail... was causing an interleaved system farm to crash" [76].

- At Los Alamos in 2003, the ASC Q supercomputer crashed regularly due to soft errors [37].

Of course, and perhaps even worse, there is always the possibility that the result of a program is incorrect. Such an outcome is referred to as *silent data corruption*. Although these issues with crashing and correctness are bad enough, transient faults can also cause some more surprising problems.

Researchers [24] have shown how an attacker can exploit transient faults to take over a Java Virtual Machine. In a Java Virtual Machine, the virtual machine runs in the same address space as the untrusted program, relying on type safety to keep the untrusted program from touching its address space. Essentially, the attacker can craft a program that waits until a fault results in a pointer with a runtime type that does not match its static type and then uses this mismatch to execute arbitrary code.

Cryptographic protocols can be broken using transient faults [7, 8, 19, 56, 4]. For example, certain implementations of RSA based on the Chinese Remainder Theorem are vulnerable to a single fault [9]. RSA relies on the inability to factor a large number N into two prime numbers p and q. A signature computed from a message m and a private key d has the form  $a * s_p + b * s_q$  where a and b are precomputed values and  $s_n$  is a function of m, d and n. If an attacker obtains two signatures (one correct, one faulty) of the same message, he can take the difference of the two signatures. One of the two terms cancels

Figure 1.1: Effects of Altitude [76] and Feature Size [11] on Transient Faults

out, leaving the difference of the other. Then by factoring out the precomputed value and calculating a greatest common divisor, the attacker can determine p and q.

#### **1.1.2 Transient Fault Trends**

It is difficult to get precise numbers on transient fault rates, but as a benchmark, in 2004, a typical laptop with 1GB DRAM had approximately 1 soft fail per year [76].

The particles that cause transient faults are mostly high-energy neutrons in cosmicray radiation [76], and so fault rates increase with altitude. The graph in Figure 1.1 shows that the amount of cosmic ray flux in Denver, Colorado is about four times that of New York City. The data was gathered over three years beginning in 1986, with New York City averaging one failure every 45 days, and Leadville averaging one failure every two days.

These results are for transient faults that affect memory. Transient faults can also affect the latches in the processor itself, and these faults are much harder to detect. Unfortunately, trends in processor manufacturing are causing these fault rates to increase over time. Faster clock rates, increasing transistor density, decreasing voltages and smaller feature sizes are resulting in processors that are more susceptible to transient faults [5, 46, 63]. For example, decreasing voltages reduce the critical voltage of each transistor, making it more likely that adding the extra charge from a fault will change a value. On the other hand, decreasing feature size makes it less likely that a fault will affect a given transistor. As a result, the fault rate per bit is expected to remain roughly constant for the next few generations [26, 31]. However, the number of transistors per chip is increasing, and so the overall result is an increase in the fault rate per processor. Figure 1.1 shows how the transient fault rate increases as the feature size decreases in a processor. Because of the combination of these factors, fault rates are increasing approximately 8% per processor generation [28].

So although the average computer user may not be aware of transient faults today, transient faults are likely to become a significant problem in the near future.

#### **1.2 Existing Transient Fault Solutions**

The computer architecture and compiler communities are well aware of the issues surrounding transient faults, and dealing with transient faults has been an active area of research for many years. At the high level, all the solutions work by adding redundancy. Redundancy can be added in time (by computing a result and then computing it again), in space (by storing values in two locations), or in information (using techniques such as checksums or error-correcting codes). The many solutions can be divided into two main categories: hardware-based solutions that duplicate hardware structures in the processor or exploit multiple cores, and software-based solutions that insert additional instructions to verify that values are not corrupted.

Chapter 5 goes into more detail on the existing solutions, but as one would expect, there are trade-offs to each type. It is standard to evaluate a system in terms of how it performs along three axes: cost, performance, and power. Transient faults add a fourth axis to be considered – reliability. Hardware solutions are generally more efficient in terms of performance, but more expensive in terms of power and cost. In addition, once a hardware solution is deployed, it cannot be changed. Software solutions, on the other hand, are more flexible. Because they are controlled by a compiler, they can be deployed when, where, and to the degree necessary. Software solutions have no additional hardware cost, but they often have a noticeable performance overhead. The reliability added by each solution varies, but it is safe to say that although hardware solutions can achieve very high rates of fault detection and recovery, software-solutions are fundamentally limited without hardware support. More recently, researchers have begun proposing hybrid solutions that use small amounts of additional hardware that is controlled by the software with the hopes that such solutions can combine the best of both worlds.

#### **1.2.1** An Example Solution: SWIFT