### EFFICIENT, SCALABLE ARCHITECTURES FOR LATTICE-GAS COMPUTATIONS

Richard K. Squier (Thesis)

CS-TR-304-91

June 1991

## **Efficient, Scalable Architectures for Lattice-Gas Computations**

Richard K. Squier

A DISSERTATION

PRESENTED TO THE FACULTY

OF PRINCETON UNIVERSITY

IN CANDIDACY FOR THE DEGREE

OF DOCTOR OF PHILOSOPHY

RECOMMENDED FOR ACCEPTANCE

BY THE DEPARTMENT OF

COMPUTER SCIENCE

JUNE 1991

© Copyright by Richard King Squier 1990 All Rights Reserved

# Efficient, Scalable Architectures for Lattice-Gas Computations —Abstract—

## Richard K. Squier Thesis Advisor - Professor Kenneth Steiglitz

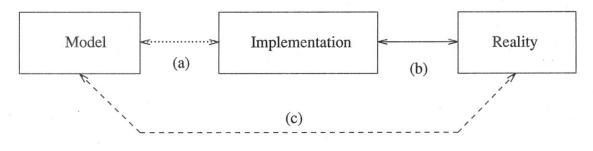

The subject of this dissertation is finding an architecture for two-dimensional cellular automata computations that is verifiably correct, and the fastest and cheapest possible. The motivating problems for this work are large-scale scientific computations; the hardware context is that of application-specific processors attached to general-purpose systems. While the conclusions are derived for a specific class of two-dimensional cellular automata, the so-called "lattice gasses," they are applicable to a wide range of similar problems.

By developing and applying solutions to discrete isoperimetric problems to a pebbling game, upper bounds on throughput for machines computing problems with data dependency graphs based on the undirected graphs for the Hardy-de Pazzis-Pomeau (HPP) and Frisch-Hasslacher-Pomeau (FHP) lattice-gasses are shown. A particular architecture, the "Wide Serial Architecture" (WSA), is shown to be within a factor of approximately 6 of the bound for the HPP-like computations, and within a factor of about 4.5 of the bound for the FHP-like computations. Besides the insight they provide into the optimal computational strategy, the methods of solution of the isoperimetric problems, such as the use of the Wulff Crystal, are of interest in their own right.

An analytic study of the least-cost configuration for a multiple-pipeline WSA machine is undertaken. The use of overlap-save method is described, and the efficiency of the WSA architecture using this method is derived. A numerical search is used to find the least cost machine configuration as the problem size is scaled. A slightly super-linear speedup is shown over a moderate range of problem sizes, and the least-cost machine parameters are described.

Finally, a data-embedded, specification-based testing technique for FHP lattice gasses is introduced. The tests consist of limit cycles in the cellular automaton, and their error detection coverage is shown empirically to be good. Their use in software, hardware, and system debugging is described, as well as their use as runtime simulation error detectors. Machine design tradeoffs relating to testability are discussed.

#### Acknowledgements

First, I want to apologize to the many people that I cannot mention in this brief acknowledgement and to whom I owe a debt of gratitude. Please accept my thanks.

I want to thank my advisor, Kenneth Steiglitz, whose insight, knowledge, advice, humor, friendship, and occasional prodding were invaluable to me. I feel very lucky to have had the opportunity to be associated with him over this time, which now seems too brief. I would like to thank Andrea LaPaugh and Joel Friedman for their patient and careful reading of this work while it was still under revision and in a very disorganized form, and of course, for their valuable comments. Also, I would like to thank Richard Lipton for suggesting I look into pebbling games, Jeane Taylor and Fred Almgren for introducing me to the Wulff Theorem, and David Dobkin for encouragement and advice in using graphics tools.

I would like to thank fellow graduate students Neal Young, for many useful discussions, Mordecai Golin, for reading portions of the thesis and offering valuable comments, and Eleftherios Koutsofios, for essential help in producing graphic displays. Also, many thanks to Adam Buchsbaum, Jeff Westbrook, Steve Kugelmass, Rob Abbott, and Heather Booth, for their helpful discussions.

I would like to thank all the staff of the Computer Science Department for the help I have received from them in many ways. Special thanks to Sharon Rodgers, Grace Kehoe, Melissa Lawson, Winnie Waring, Stephen Beck, and Ed Strong.

Finally, I would like to thank my family and friends who gave me their encouragement and support.

Richard K. Squier Princeton, New Jersey 17 January 1991

This work was supported in part by NSF Grant MIP-8912100, by U.S. Army Research Office - Durham Contract DAAL03-89-K-0074, by DARPA/ONR Contract N00014-88-K-0459, and by a Von Neumann Fellowship in Supercomputing.

Chapter 4 of this thesis was published previously in short form in *Proceedings of the International Conference on Application Specific Array Processors*, see [61].

#### **Table of Contents**

| Abstract                                                             | j   |

|----------------------------------------------------------------------|-----|

| Acknowledgement                                                      | i   |

| Table of Contents                                                    | iii |

| Chapter 1. Introduction                                              | 1   |

| 1.1 Introduction                                                     | 1   |

| 1.2 Lattice-Gas Automata                                             | 2   |

| 1.3 The WSA Architecture                                             | 5   |

| 1.4 Thesis Outline                                                   | 6   |

| Chapter 2. Upper Bounding Throughput and A Nearly Optimal Archi-     |     |

| tecture                                                              | 8   |

| 2.1 Introduction                                                     | 8   |

| 2.2 The Formal Basis for Input/Output Bounds                         | 16  |

| 2.2.1 The Parallel Red-Blue Pebble Game                              | 16  |

| 2.2.2 Dependency Graph Partitioning and Partition Element Esti-      |     |

| mators                                                               | 21  |

| 2.3 The I/O Bound from the Maximum Kernel Size                       | 31  |

| 2.3.1 Bounding the Size of the Dependency of a Set                   | 32  |

| 2.3.2 Size of the Dependency for the Discrete Torus                  | 46  |

| 2.3.3 Standard Spheres for the Triangular Lattice                    | 62  |

| 2.4 Applying the Pebbling Bounds to Measure Architectural Optimality |     |

|                                                                      | 73  |

| 2.5 Summary, Conclusions, and Future Work                            | 84  |

| Chapter 3. Optimal Machine Scaling                                   | 88  |

| 3.1 Introduction                                                     | 88  |

| 3.2 Speedup and Cost                                                 | 89  |

| 3.3 Overlap-Save Method                                              | 91  |

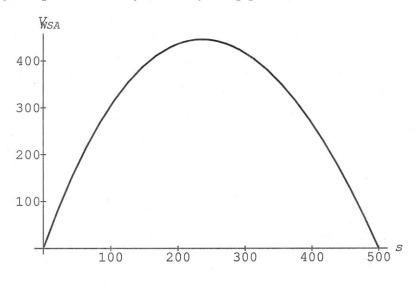

| 3.4 Overlap-Save Applied to WSA                        | 91  |  |  |

|--------------------------------------------------------|-----|--|--|

| 3.5 WSA Efficiency and Throughput                      | 96  |  |  |

| 3.6 Scaling Resources                                  | 99  |  |  |

| 3.7 The Cost and Objective Functions                   | 104 |  |  |

| 3.8 Analysis                                           | 108 |  |  |

| 3.9 Summary, Conclusions, and Future Work              | 118 |  |  |

| Chapter 4. Testing Parallel Lattice-Gas Simulators     | 121 |  |  |

| 4.1 Introduction                                       | 121 |  |  |

| 4.1.1 Lattice-gas Automata                             | 123 |  |  |

| 4.1.2 Definitions and Notation                         | 128 |  |  |

| 4.2 Test Sets and Their Constituents                   | 129 |  |  |

| 4.3 A Test Pattern                                     | 131 |  |  |

| 4.4 Constructing a Test Cycle                          | 134 |  |  |

| 4.5 Error Detection and Experimental Results           | 138 |  |  |

| 4.5.1 Detection Difficulties                           | 141 |  |  |

| 4.5.2 Experimental Results                             | 143 |  |  |

| 4.6 Architectures and Applicability of the Test Method | 143 |  |  |

| 4.7 Summary and Conclusions                            | 145 |  |  |

| Chapter 5. Conclusion                                  | 149 |  |  |

| Appendix A. Supergraph Complexity Theorem              | 157 |  |  |

| Appendix B. Test Pattern Library                       |     |  |  |

| References                                             | 178 |  |  |

## Chapter 1 Introduction

#### 1.1. Introduction

The subject of this dissertation is finding an architecture for two-dimensional lattice-based computations that is verifiably correct, and the fastest and cheapest possible. The motivating problems for this work are large-scale scientific computations; the hardware context is that of application-specific processors attached to general-purpose systems. The results presented here are arrived at by mathematical study of tradeoffs between machine resources and throughput (Chapter 2), by analytic and numerical studies of the tradeoffs between cost of construction and throughput (Chapter 3), and by empirical development of a tradeoff between verifiability of implementation correctness and certain design factors (Chapter 4). While the conclusions are derived for a specific class of two-dimensional cellular automata, the so-called "lattice gasses," they are applicable to a wide range of similar problems, including local iteration algorithms for differential equations.

Two areas of recent development have driven this work: theoretical results on cellular automata properties for complex system modeling, and technology for inexpensive custom VLSI. The theoretical understanding of the properties of certain simple cellular automata has made them interesting candidates for investigating complex systems by simulation study using these automata. There are two basic reasons why they are promising: (1) they avoid certain problems of instability and system definition encountered in the usual numerical approach to modeling complex systems, and (2) the cellular automata computing paradigm is inherently parallel with simple communication which suggests that large-scale parallel machines may be easier to build under this paradigm than others.

The rapid advance of VLSI technology in such directions as silicon compilers; cheaper, denser, and faster chip technology; and rapid prototyping suggests that, in the near future, building algorithm-specific adjunct hardware will become increasingly cost-effective. In general, simulation studies using cellular automata, such as latticegas simulations, require the simulation of automata with a very large number of cells for many iterations. This type of computation is generally beyond the capabilities of conventional general-purpose machines, and in the scales proposed, beyond the reach of today's super-computers. However, the developments in VLSI technology may

make special-purpose hardware for the simulation of specific cellular automata practical.

It is becoming accepted that no single architecture is equally applicable to all algorithms. In the field of parallel computing, it is not uncommon to find that an algorithm which is efficient on one parallel architecture is inefficient on another. In the application-specific array community there is currently work proving various particular architectural organizations are optimal for the particular algorithm they implement. This dissertation answers some questions of optimality for the lattice-gas algorithm, and suggests directions for future work that might lead to a more general strategy for deriving an optimal architecture from an algorithm. The hope that studying the specific lattice-gas algorithm will teach us about implementing other algorithms affects our problem formulations, and colors the entire work in many ways.

The remainder of this chapter is organized as follows. Section 2 describes the lattice-gas automata; Section 3 gives a summary of results found in the thesis.

#### 1.2. Lattice-Gas Automata

In cellular automata, values associated with nodes in an undirected graph are updated in synchronous steps according to a rule (the rule may, or may not, be uniform for every node) applied locally at each node. The edges of the graph define which nodes are "neighbors" of a node, and the update rule determines the new value of the node from the values of its neighbors and itself.

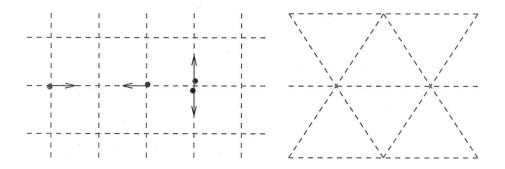

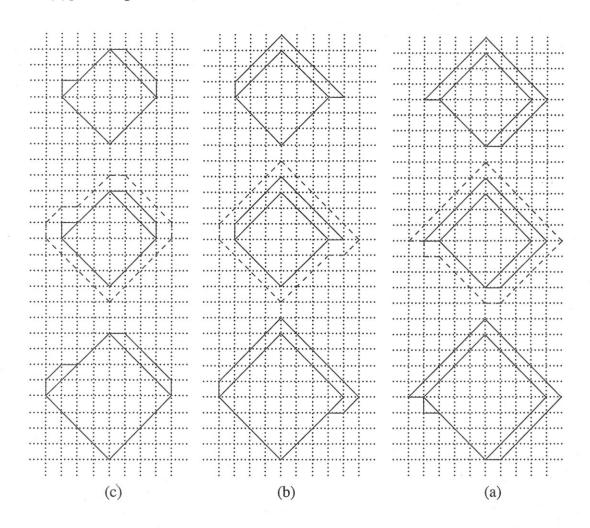

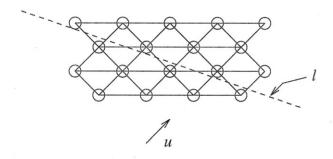

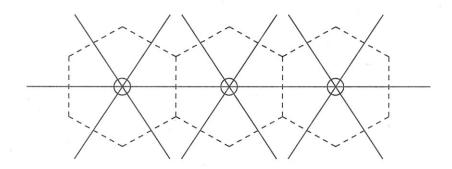

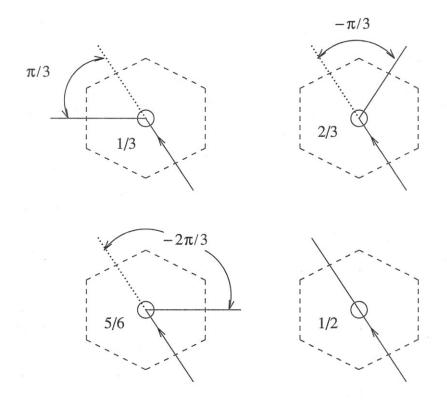

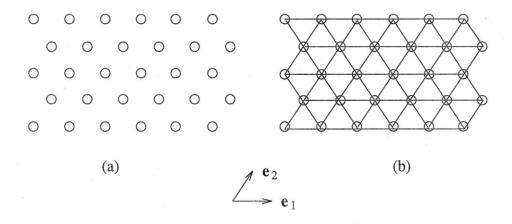

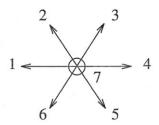

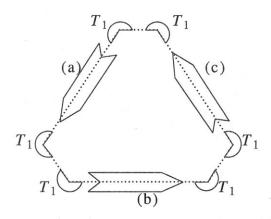

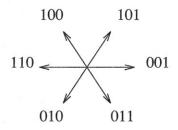

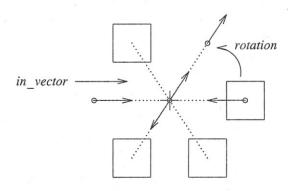

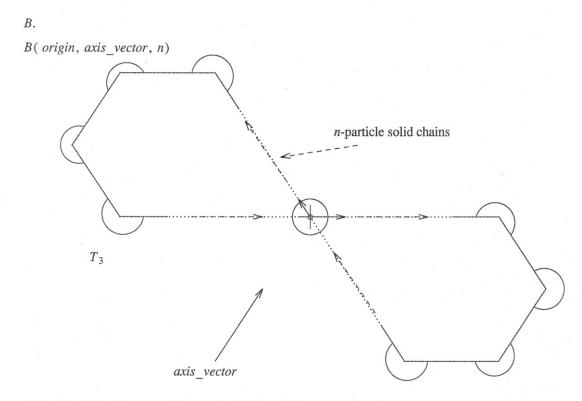

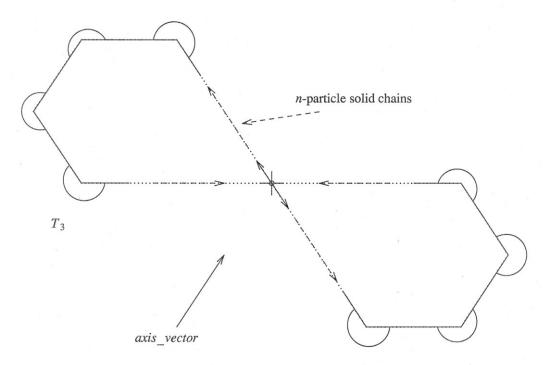

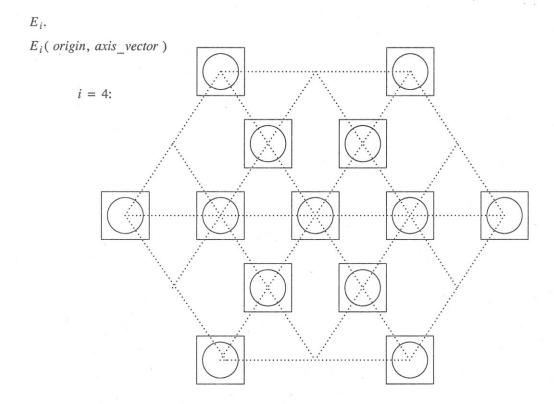

A lattice-gas automaton is a cellular automaton whose neighbor-defining graph is a lattice graph. (For a precise definition of a lattice graph, see [1].) The rule defining a lattice-gas automaton's evolution generally simulates particles traveling along the edges of the neighbor graph. Our version of a lattice gas is based on the HPP and FHP-III models as described in [2, 3] (see figure 1.1). The FHP models are of interest because they have been shown to correspond to the Navier-Stokes equations for fluid flow. The HPP models are interesting partly because of their modelling ability, and partly because the general form of their data dependency graphs conform to the data dependency graphs of a general class of iterated problems. These types of lattice-gas automata (FHP and HPP) consist of a two-dimensional lattice graph and a set of update rules for variables associated with each node in the lattice graph. The lattice is the integer grid, for the HPP gas, or the triangular lattice, for the FHP gas. The edges of the lattice graph connect nearest neighbors in the lattice (this can be extended by also connecting next-nearest neighbors and so forth), resulting in the two-dimensional grid

figure 1.1.

The lattice graphs for the HPP lattice gas (left) and the FHP lattice gas (right). Dashed lines represent undirected edges in the graph, and the intersections of the dashed lines represent nodes. On the left of the HPP example, two particles are shown about to collide at a node; on the right, two particles are exiting a node after a similar collision.

in the HPP case, and the triangular lattice graph in the FHP case. These graphs may be embedded on the surface of a torus, or in the plane. At each site each incident edge has an associated variable representing the presence or absence of a unit mass particle with unit velocity directed toward the site's neighbor along that edge. An additional dynamical variable can be used to encode the presence or absence of a unit mass particle with zero velocity positioned at the lattice site (called a "rest-particle"). With this interpretation of the variables the update rule is designed so that, letting the edges have unit length, the lattice is populated with particles traveling along graph edges and colliding at lattice sites. Figure 1.1 shows a small section of an HPP lattice gas with several particles, and a small section of an FHP lattice graph without particles.

For the lattice gasses the automaton update rule table is called a collision rule set, the initial configuration of states determining a cell's new state is called a collision, the next state entry in the rule table is called the result of the collision, and the combination of a collision and its result is called a collision rule. A particular lattice gas is defined by specifying a collision rule set that gives the results of every possible collision. These rules can be thought of as rules about the action of particles (variables set to one) or equivalently as rules about the action of holes (variables set to zero), as they collide at lattice sites. In an HPP or FHP gas, particle collisions generally conserve momentum and mass, are symmetric with respect to rotation by integer multiples of the basic angle of the lattice, and are symmetric for time reversal; for the FHP-III gas, collisions are also symmetric with respect to hole/particle duality (complementation of the dynamical variables).

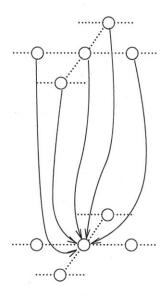

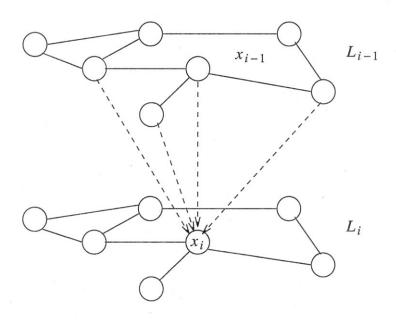

A data dependency graph for the evolution of an automaton is a layered graph, each layer being a replica of the set of nodes of the automaton's undirected lattice graph, there being as many layers as there are total steps in the automaton's evolution. Directed edges in the data dependency graph indicate which values were used to compute new values, so arcs go from layer to layer, indicating the state of the automaton at one step is derived from its state at a previous step.

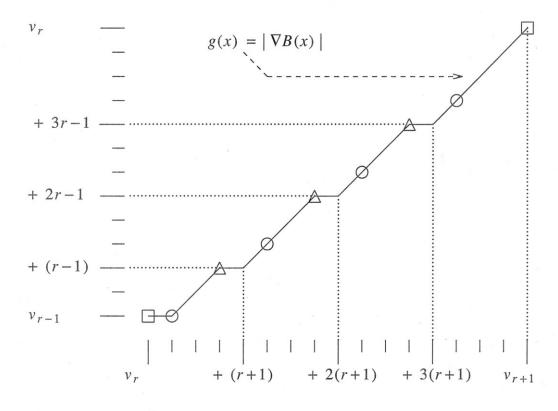

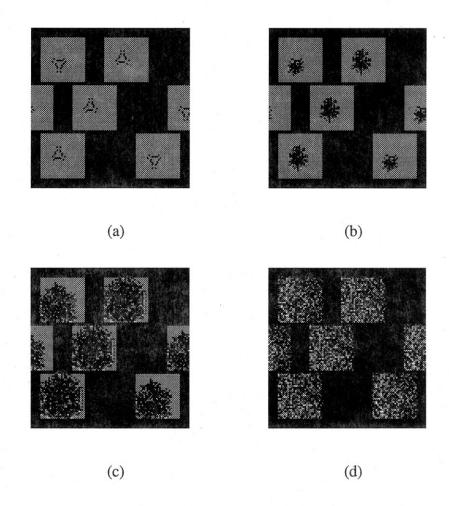

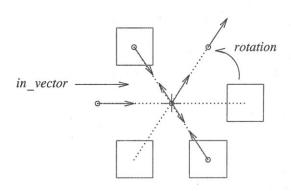

figure 1.2.

The dependency arcs in the data dependency graph for an update of a single in node in an HPP lattice. The dotted lines show the embedding of the HPP lattice graph in the layers of the data dependency graph.

Figure 1.2 shows the dependency arcs from the neighborhood of one node to the updated node in the next layer in a data dependency graph for an HPP simulation. Data dependency graphs for many other iterated computations are similar in that, even though they may not be layered in the strict sense, they may still have a structure similar to layering in that the there is some connected graph implicitly defined that can be used to define a layered subgraph. Since many of our results are based solely on the graph structure of a particular data dependency graph, the results apply to any computation whose data dependency graph contains a similar sub-graph.

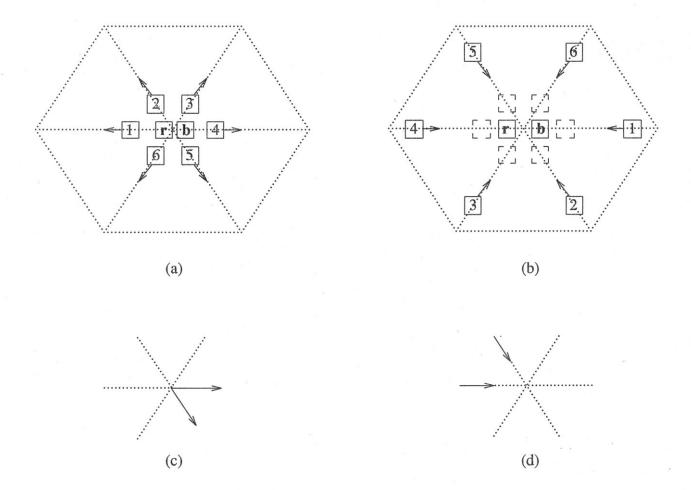

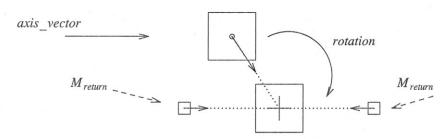

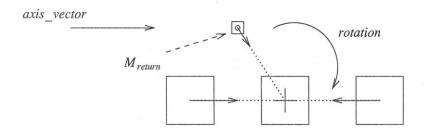

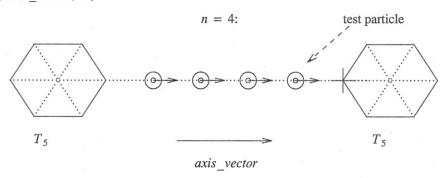

#### 1.3. The WSA Architecture

Since a considerable part of this work concerns the WSA architecture, we present here the logical organization of the computation used by that architecture.

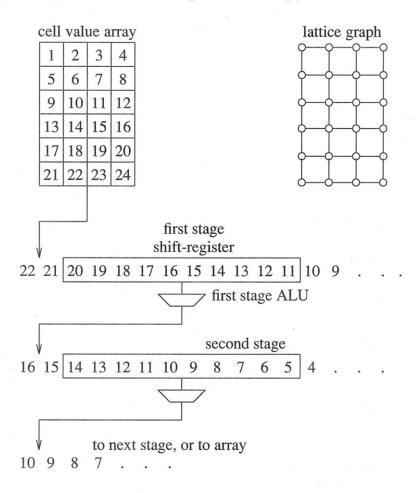

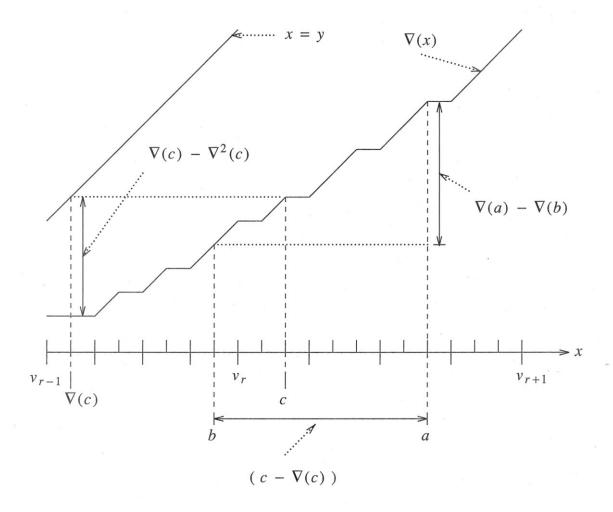

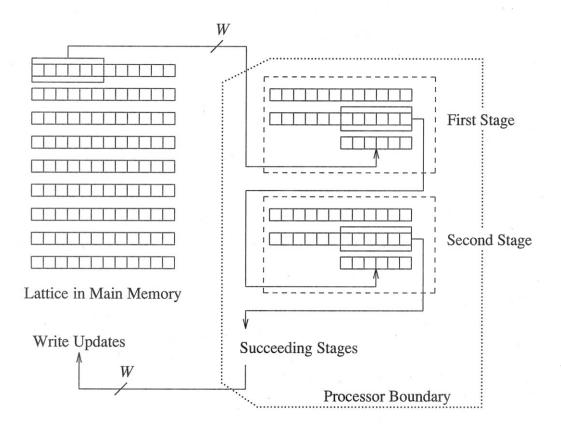

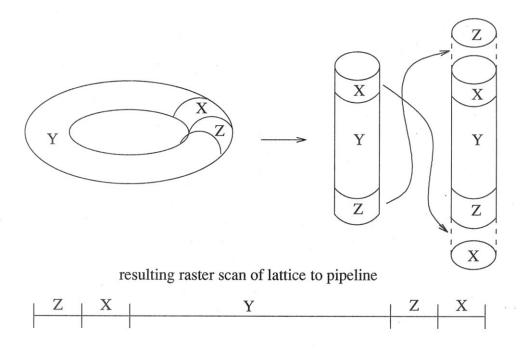

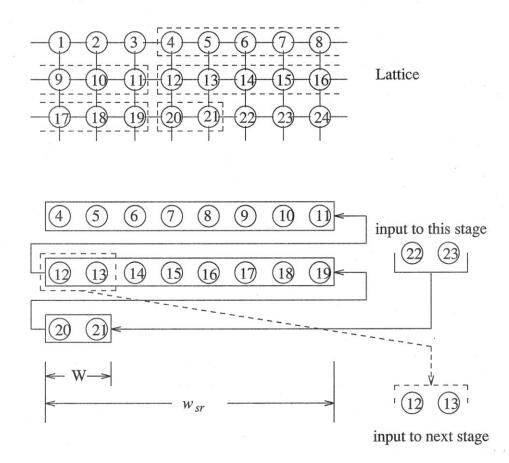

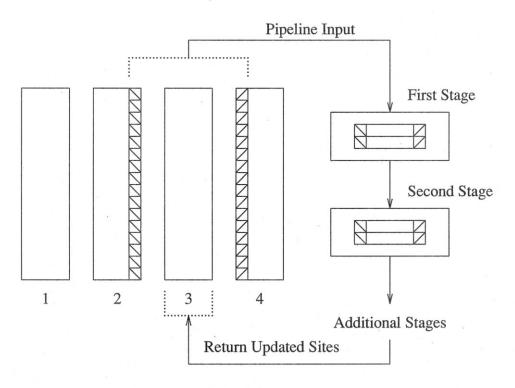

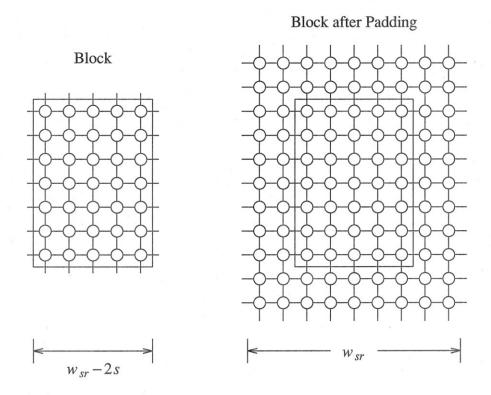

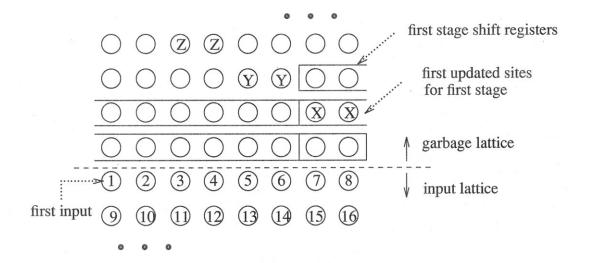

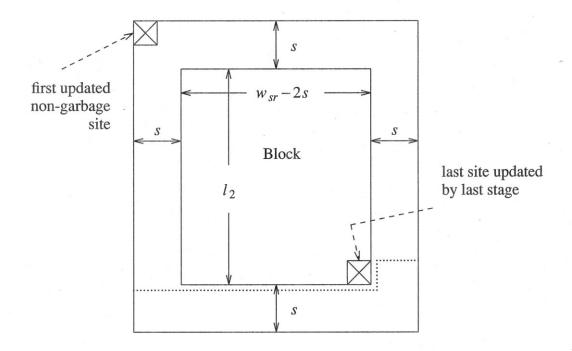

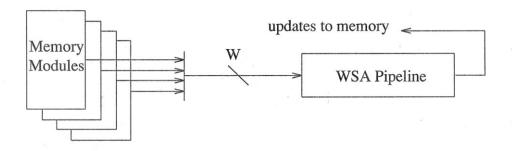

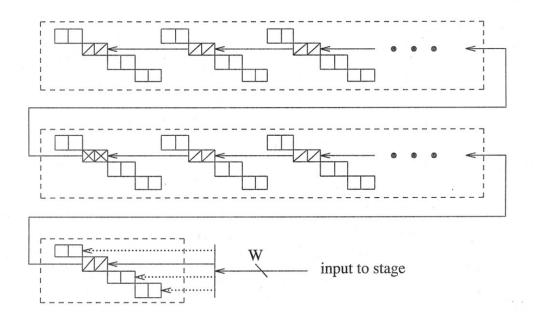

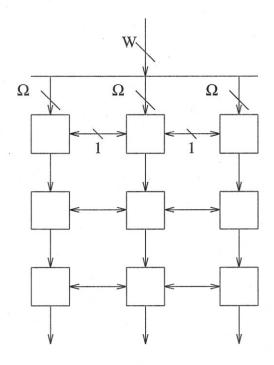

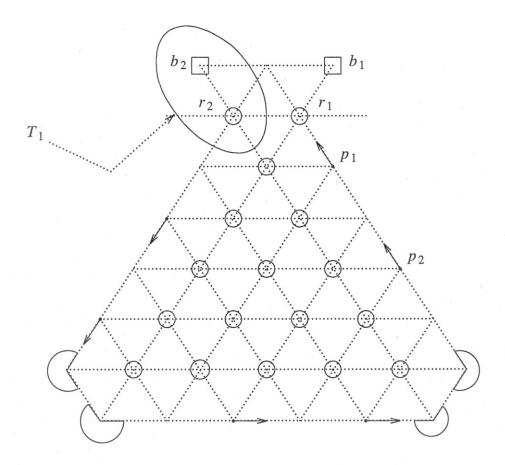

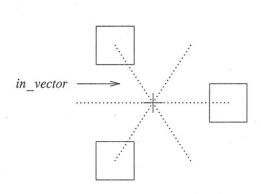

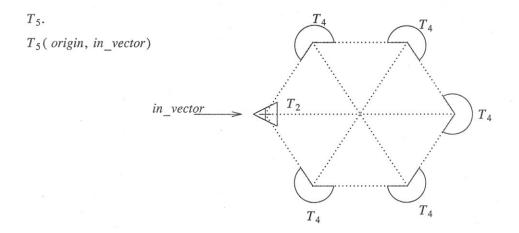

figure 1.3.

The logical organization of computation in the WSA architecture. At the top left is shown an array of site values corresponding to the HPP lattice graph shown at upper right. The lattice site values are passed to the pipeline stages below the array. Here, the first stage is producing updated values for sites 15 and 16, which are being passed on to the second stage. The first stage's shift-register contains site values for sites 11 through 20. The second stage is producing values for sites 9 and 10 which are updated by two automaton evolution steps from the values originally stored in the array.

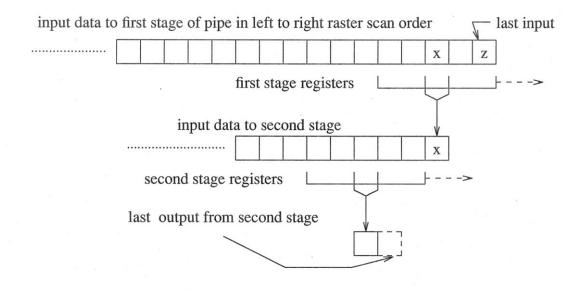

The WSA architecture updates the state of a lattice-gas automaton by passing the state of the lattice through a pipeline. All the stages of the pipe are identical, and each stage produces lattice site values that are updated one generation from the stage's input values (see figure 1.3). The first stage of the pipe receives the lattice site values in raster scan order from the memory, and passes updated lattice site values in the same

raster scan order to the following pipe stage. When the complete array of values has been scanned through the first stage, the entire lattice will have been updated one automaton evolution step by the first stage. As each stage is identical, the output from the second stage will be the lattice updated two steps, and if there are *s* stages in the the pipeline, the lattice values exiting the pipe and being returned to the array will be the values of the lattice updated *s* steps. The "width" of the architecture is determined by the number of lattice site values passed along the pipeline from one stage to the next in one global machine tick, or cycle. In figure 1.3, the width is 2 since each stage produces two site values simultaneously. We will go into further details of the WSA architecture, and the LGM-1 machine based on this architecture, in succeeding chapters when the discussion requires it.

#### 1.4. Thesis Outline

Chapter 1 is this introduction. Chapter 2 develops an upper bound on throughput for machines computing problems with data dependency graphs based on the undirected graphs for the HPP and FHP lattice-gasses. Using these bounds, a particular architecture (WSA) is shown to be within a factor of approximately 6 of the bound for the HPP-like computations, and within a factor of about 4.5 of the bound for the FHP-like computations. This work extends previous work by making detailed definitions and refining the means of estimation. The result is increased insight into the nature of the constraints limiting throughput. Because Chapter 2 is rather lengthy, we give a brief summary below.

#### Outline of Chapter 2

#### Formal Basis for Input/Output Costs

A pebbling game is an analytical tool for modelling resource usage by a computation. The game is played on the associated data dependency graph, the pebbles representing machine storage registers. A pebble placed on a node is interpreted as indicating the value associated with the node is stored in the register associated with the pebble. This section introduces a new variant of the red-blue pebbling game, and shows that it models any computation of a parallel machine with fixed resources of input/output (I/O) bandwidth and storage. This section defines precise characterizations of the state of the pebbling game as it progresses, and proves, for this new pebbling game, two strengthened theorems similar to ones previously shown for the original red-blue pebbling game: the Partitioning Theorem, and the Dominator Theorem. These two theorems provide the basis for making I/O cost estimates using the new pebbling game by providing a

characterization of sets of nodes in the data dependency graph of equal I/O cost.

#### Bounding the Size of the Estimators

This section proves two essential theorems: the Dependency Symmetrization Theorem, and the Dependency Collapsing Theorem. When making size estimates of the maximum size of the node sets mentioned in the first section, these two theorems taken together allow the assumption that the node sets have a canonical shape. Using previous work on discrete isoperimetric inequalities for the discrete torus, the exact form of these maximum sized sets is found for the HPP-like computations. Using previous work for continuous isoperimetric extremal sets, the use of the Wulff Crystal is introduced to solve the discrete isoperimetric problem for the FHP-like computations.

#### Nearly Optimal Architecture

Using the bounds on set sizes mentioned in the previous section, throughput bounds are derived in this section, and compared with the throughput of the WSA architecture for HPP- and FHP-like computations, showing that this architecture is nearly optimal.

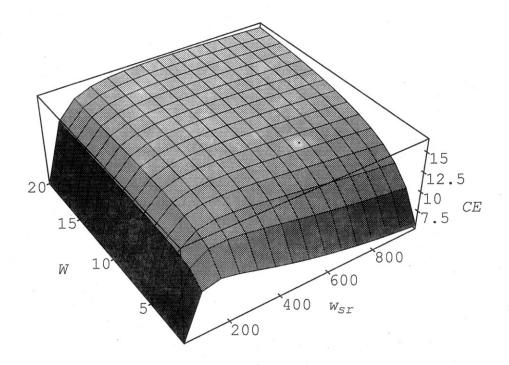

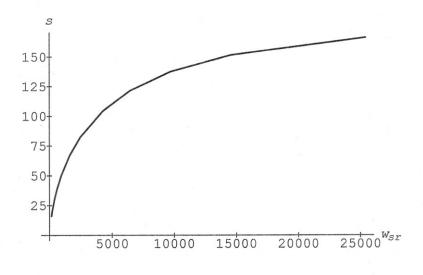

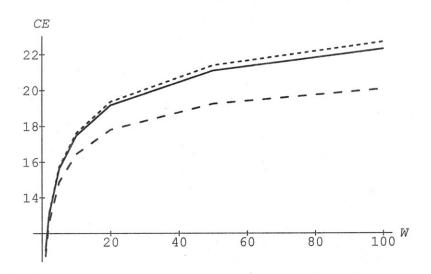

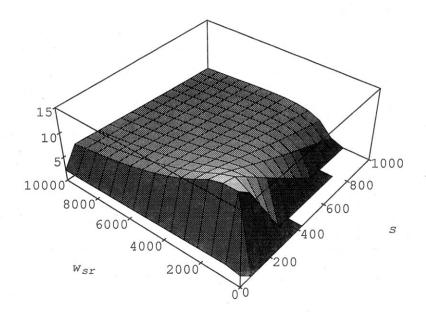

Chapter 3 is an analytic and numerical study of the least-cost configuration for a WSA-type machine when problem scaling is required. The use of overlap-save method is described, and the efficiency of the WSA architecture using this method is derived. A linear cost function is derived for a completely scalable WSA-type machine. A numerical search is used to find the least cost machine configuration as the problem size is scaled under the constant-time assumption. A slightly super-linear speedup is shown over a moderate range of problem sizes. The least-cost machine parameters are described.

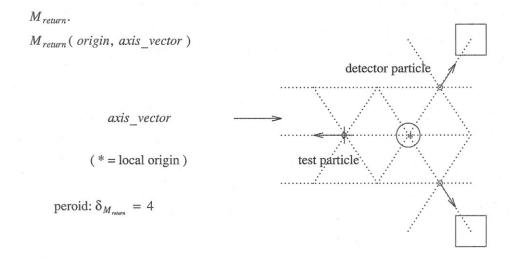

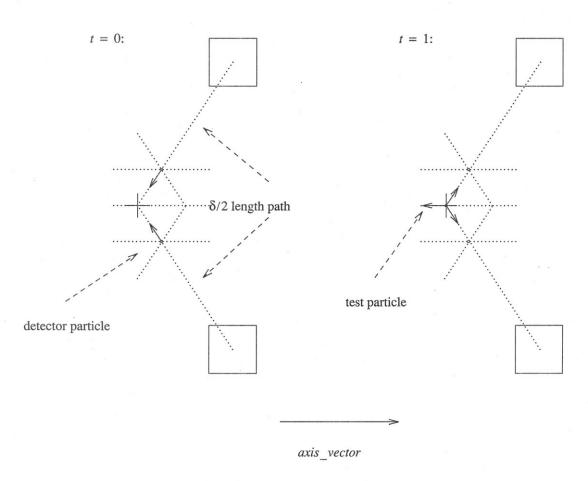

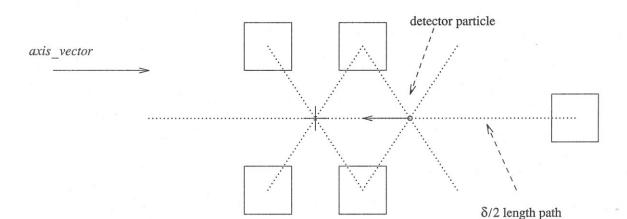

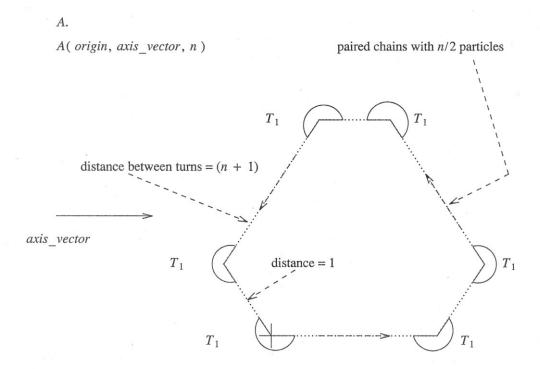

Chapter 4 introduces a data-embedded, specification-based testing technique for FHP lattice gasses. The tests consist of limit cycles in the cellular automaton. Their error detection coverage is shown empirically to be good. Their use in software, hardware, and system debugging is described, as well as their use as runtime simulation error detectors. A trade-off between the number of "frames" in the design of the cellular-automaton simulating machine and its amenability to this type of testing is discussed.

#### Chapter 2

#### Upper Bounding Throughput and A Nearly Optimal Architecture

#### 2.1. Introduction

Ever since von Neumann and Ulam invented cellular automata [4], computing under this paradigm has been looked on with optimism because it appears to facilitate a high degree of parallelism. If cellular automata simulations can be effectively parallelized, methods which can be formulated as cellular automata computations have an advantage over those that cannot be similarly parallelized. Particular examples of such computational methods are the cellular automata known as lattice gasses, which are important candidates as substitutes for other, less easily parallelized computational methods used in such problem domains as fluid dynamics. Unfortunately, cellular automata simulations have as yet been unable to fulfill completely the hopes held for them, even though there have been some machines built specifically for their simulation, for two principal reasons. The first, which we will not address here, is that the theoretical understanding of complex systems has not matured to the point where such systems can be modeled by cellular automata with quantitatively predictable results. The second reason for the slow progress of cellular computing is that sufficiently powerful hardware has not been available.

The need for hardware with very high throughput for cellular automata simulation is mostly a consequence of the sizes of the simulated automata. For instance, it has become clear that applying lattice-gas simulation to interesting problems requires the use of automata with a very large number of cells [60], and therefore its effectiveness is dependent upon employing inexpensive, highly-parallel, special-purpose hardware. Because of the simplicity of the cellular computing paradigm, one would expect that simulators for cellular automata, and especially for lattice-gasses, should be able to use the inexpensive logical functionality provided by VLSI technology to achieve cost-effective performance. However, hardware with sufficient power to simulate large cellular automata is, as yet, still not cost-effective. The principal shortcoming, as we will show below, is that it is not possible to devote the majority of the processor's VLSI real-estate to usable logical functionality. The aim of this chapter is to identify and quantify the factors limiting the effectiveness of hardware resources in lattice-gas simulators.

The goal in designing special purpose hardware for simulating lattice-gas automata —assuming there is no computational shortcut to determining the automaton's future state— is to maximize the throughput for the automaton simulation given the architectural resource constraints. The most appealing idea for a lattice-gas simulating machine, or other cellular automata simulator, is a machine with a single processor for every cell of the automaton. In such a machine communication is strictly local: processors communicate only with processors assigned to neighboring cells of the automaton. This aspect of cellular automata, local communication, has been singled out as one of the fundamental advantages that cellular automata offer [5]. However, because the lattices often must be large for these simulations to achieve interesting behavior, and because the present technology limits our ability to interconnect and synchronize such large physical arrays, the usual approach to special purpose hardware has been to scan the lattice data through some sort of processor that updates the sites' states. That is, the current state of the automaton is held in some memory device and portions of the automaton state are passed to some hardware that updates the cells until a new state has been computed for every cell of the automaton.

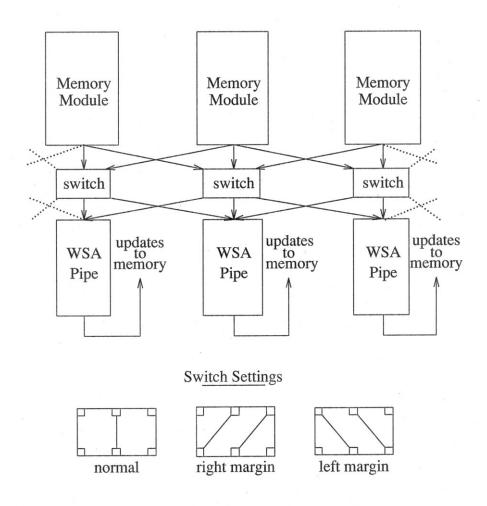

Up to now, almost all special-purpose cellular automata machines built have used a scanning approach, and are similar in their basic logical organization of communication and processing. For a fairly comprehensive list of examples from CELLSCAN (1960) to Cytocomputer (1989), see [6]. There has also been a multitude of activity in this area in the systolic array literature, see [7] for examples, and see [8] for a description of the RAP1 machine which was built specifically with simulating lattice-gas automata in mind. Some machines have been designed to closely approximate the oneprocessor-per-cell concept, such as the Connection Machine [9], and the general cellular automaton simulating machine, CAM [5]. However, because it is overly restrictive in practice to add more hardware whenever one has an automaton simulation problem larger than the current machine can accommodate, these types of machines must resort to a scanning strategy when the problem size becomes large enough. Therefore, we will focus our attention on the class of special-purpose cellular automata simulators of the scanning type. The particular architecture we will concentrate on, the LGM-1 architecture [10], is one devised specifically for simulating lattice-gas automata, and is a scanning type of architecture employing custom VLSI chips for the update processors.

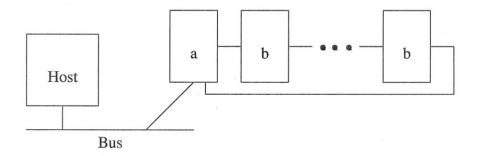

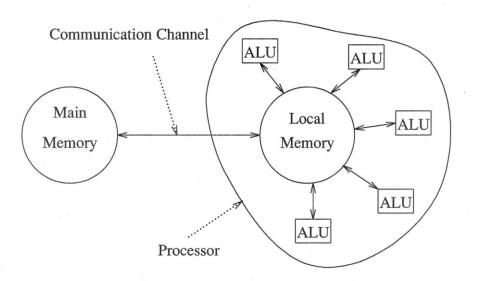

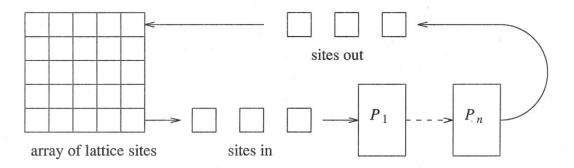

Let us make the discussion concrete by looking more closely at the LGM-1 machine. Figure 2.1 shows the top level organization of the machine (we will describe it in more detail later). The lattice-site state values are stored in the host machine, in

figure 2.1.

The LGM-1 machine organization. (a) is a bus interface board, and (b) represents processors boards containing ten custom VLSI chips each.

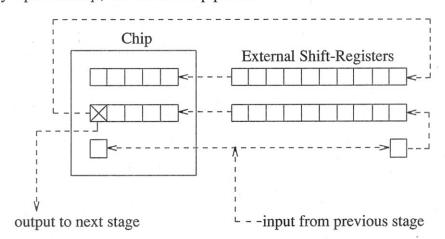

this case a Sun 3/160C<sup>†</sup>, and passed to the custom hardware over the VME bus. The updated site values are passed back over the bus to the host. The custom chips are arranged in a linear pipeline so that the output of one chip feeds the input of the next chip; the two end chips communicate with the host via bus interface logic. Repeatedly scanning the lattice array produces further global updates of the automaton state. Every custom chip in the processor updates the automaton state by one generation. The LGM-1 machine is extensible so that adding more chips increases the throughput: an n-chip machine has nearly n-times the throughput of a one-chip configuration.

Table 2.1 shows the measured performance of the LGM-1 machine and its host. The performance was measured for three different software C language drivers running on the host:  $run\_ca$ , cpu.SFM, and cpu.LOCAL. Each of these drivers was also measured in an optimized form: INLINE indicates that all procedure calls were eliminated by putting the procedure code inline, O2 indicates the code was compiled using an optimizing compiler, and UNR indicates that the code is 256-fold loop unrolled. The  $run\_ca.MON$  code was compiled with a profiler. The  $run\_ca$  code is the driver for the LGM-1 pipeline hardware. This code does all the host data handling duties for the custom boards and controls board operation via the VME bus: the code runs on the host and writes data and control words to the VME bus and on to the custom hardware; the results are collected by reading the output register of the custom hardware via the same route. Each cycle of the pipeline requires two 16-bit writes and one 16-bit read. This code is responsible for configuring the lattice data into slices 256 sites wide that are

<sup>†</sup> Sun is a trademark of Sun Micro Systems, Incorporated.

|                    | site updates  | effective interface bandwidth |                   |  |  |

|--------------------|---------------|-------------------------------|-------------------|--|--|

| code               |               | data rate                     | total bus traffic |  |  |

|                    | (M sites/sec) | (M sites/sec)                 | (M bits/sec)      |  |  |

| run_ca.MON         | 0.0941        | 0.188                         | 2.26              |  |  |

| run_ca.INLINE.O2   | 0.201         | 0.402                         | 4.82              |  |  |

| cpu.SFM            | 0.214         | 0.429                         | 5.15              |  |  |

| cpu.SFMUNR.O2      | 0.578         | 1.16                          | 13.9              |  |  |

| cpu.LOCAL          | 0.0           | 0.684                         | 8.21              |  |  |

| cpu.LOCUNR.O2      | 0.0           | 1.43                          | 17.1              |  |  |

| run_ca.MON profile |               |                               |                   |  |  |

| function           | %             | msec/call                     | total time        |  |  |

| ca_pipe            | 48%           | 130                           | 260               |  |  |

| build_strip        | 26%           | 68                            | 136               |  |  |

| unpack_strip       | 25%           | 67                            | 134               |  |  |

table 2.1.

LGM-1 measured computation and bandwidth performance ( $M \equiv 10^6$ ). LGM-1 is configured as a one-stage pipeline. The bus traffic figures for the LOCAL and LOCUNR.02 codes are projections for comparison purposes only.

passed consecutively to the custom hardware, and rebuilding the lattice as the results return from the hardware. As the profile above shows, these slicing (build\_strip) and rebuilding (unpack\_strip) functions account for about one-half the total work done by the host. For comparison's sake, results are shown for the two cpu codes, which consist of only the five core instructions from the run\_ca main loop. These codes do no computation and no data rearranging: for the cpu.LOCAL code the reads and writes are always to the same locations locally on the host; for the cpu.SFM code communication is between local variables and the custom hardware registers.

From table 2.1 we see that the host can provide at most 0.402 M sites/sec bandwidth to the custom boards when the host is also required to manipulate the storage location of the data (run\_ca.INLINE.O2). Even when the host's only job is to

step through memory and pass data back and forth to the custom boards, the peak rate is still only 1.16 M sites/sec (cpu.SFMUNR.O2), which is nearly the peak rate at which it can read and write it's own memory (cpu.LOCUNR.O2). We will assume the maximum data channel capacity between the host and the custom boards is 1.16 M sites/sec.

Consider the following facts about LGM-1.

- (1) The custom chips can run reliably at at least 7 Mhz. Each chip contains storage for 518 lattice sites, and two programmed logic arrays (PLA's) that perform the update operations. At every tick of the global clock, each custom chip (i) reads two lattice site values from its input pins, (ii) produces two updated lattice site values, and (iii) writes two lattice site values to its output pins.

- (2) The host can deliver at most 1.16 M sites/sec in bandwidth to the custom hardware: one two-site read, one two-site write, and one global clock pulse at a time.

- (3) Using the minimum local storage per PLA (seven lattice sites), the area of the chip could hold 10 PLA's with their local data.

Looking at (3) it seems plausible that one could build, using the same technology, custom chips with ten PLA's per chip running at 7 Mhz and get  $2 \cdot 10 \cdot (7 \text{ Mhz}) = 140 \text{ M}$  site-updates/sec per chip. In contrast, the actual measured computation rate is about one three-hundredth of this at 0.508 M site-updates/sec. Even without adding processors to the custom chips, as LGM-1 is presently constructed, clocking the chips at 7 Mhz leaves them idle for more than 10 local clock ticks for every global clock signal received via the bus. Is it possible that by using the local storage more effectively and reordering the computation and data access pattern we could use these idle periods to compute ten times more updates before sending the site values back to the host? If we packed ten PLA's onto each chip, and reorganized in just the right way the data sent to the chips, could we get 140 M site-updates/sec per chip performance? The general question posed by these questions is, how effectively does LGM-1 use its resources?

In this paper we develop a measure of optimality for scanning type architectures with respect to two resource constraints, main storage bandwidth and local storage capacity, that tells quantitatively how well an architecture makes use of its resources for the lattice-gas simulation problem. That is, we will answer whether or not the throughput of LGM-1 could have been considerably improved by some clever computational strategy. In particular, we show that the linear pipeline, as defined by the

LGM-1 architecture, approaches a bounding throughput value to within a small constant. This suggests that this architecture nearly achieves, or perhaps does achieve, the maximum throughput possible given the constraints on memory bandwidth and local storage regardless of the speed, computational power, number, or intercommunication network of the processors in any parallel machine computing the lattice computation.

#### **Background**

Because the structures of the data dependency graphs for cellular automata computations are independent of the input data, the data dependency graph is a particularly useful characterization of a computation for developing insight into the inherent limitations of the computation. This is done by modeling and analyzing the effects of machine resources on the computation of the nodes of the data dependency graph without regard to the values the nodes represent. The resources we have identified above can be divided into three categories: communication, storage, and computation. Here we review some of the methods used in analyzing data dependency graphs, along with some related work specifically dealing with I/O communication requirements.

Perhaps the first factor to consider in analyzing the effect of resources on the computation of a cellular automaton simulation, is the number of processors. Assuming processors are the only resource, Theorem 1 of the software analysis of Eager, Zahorjan, and Lazowska [11], leads to two conclusions. One is that, in simulating a cellular automaton with K cells, on average no more than K processors can be kept busy simultaneously. The other conclusion is that, if storage and communication are unlimited, then n processors can be kept simultaneously busy without delays, provided n is less than K. That is, if a simulation requires time t using one processor, then a machine with t processors can complete the same simulation in time t/n (with the above restriction on t). Referring to our earlier look at LGM-1, this suggests that either LGM-1 can be sped up linearly by using more processors more intelligently, or resources other than processing power are the limiting factors.

The effects of communication resources have been studied in several different ways. The effect of hierarchical communication has been studied by using variations of the general idea of extending the PRAM model by charging log(i) for accessing the data item at the  $i^{th}$  address. See Aggarwal, Alpern, Chandra, and Snir [12] and Aggarwal, Chandra and Snir [13]. Instead of separating communication into hierarchies by the above approach, communication can be divided into just two components: communication local to the machine, and I/O. This leads to the consideration of the

effect of I/O complexity. For example, Aggarwal and Vitter [14] use a counting argument on the number of permutations possible using M units of internal storage and assuming I/O communication is in blocks of size B, to determine a bound on the minimum I/O required for sorting and related problems. In an approach that is similar to pebbling, Papadimitriou and Ullman [15] develop tradeoffs between the total I/O and the time in a parallel processing environment. Other work on communication complexity is exemplified by the recent paper by Lovász and Saks [16] which addresses the communication required between processors jointly sharing the computation of some function.

The effects of limited storage locally available to the processing machine has been studied by using various pebbling games. For instance, the articles by Lengauer and Tarjan [17, 18] give storage-space/time tradeoffs for several families of data dependency graphs. See the article by Pippenger [19] for a general summary of traditional pebbling analysis.

The combined importance of communication and local storage has been recognized for a long time, and, as was pointed out by H.T. Kung in [20], is especially important for high-speed special-purpose hardware. In [21] he and Hong devised a pebbling game that models the effects of these resources on computational power. The red-blue pebble game described there models the computation and I/O steps in a sequential computation. They used it to get space-I/O tradeoffs for several problems, and to get upper bounds on speed-up of a computation of these problems using a sequential machine. The red-blue pebble game they describe was extended by Savage and Vitter [22] to the parallel-red and the block-red-blue pebble games, which model parallel computation without I/O, and with block-parallel I/O respectively.

In [23] Kugelmass, Squier, and Steiglitz introduced a further refinement of the red-blue pebble game that allows arbitrary computation and I/O parallelism. Based on this work Lopresti and Nodine [24] developed a lower bound on the the I/O requirements for simulating the "Life" cellular automaton [25], and applied this bound to several computational schemes for employing an n by n processor array.

#### **Chapter Outline**

The goal of this chapter is to find an upper bound on throughput for computing the evolution of a lattice-gas automaton, which we can use to compare with the performance of LGM-1 (or any other machine) to determine whether the machine's resources have been used to maximum potential. As we mentioned above, limiting factors are

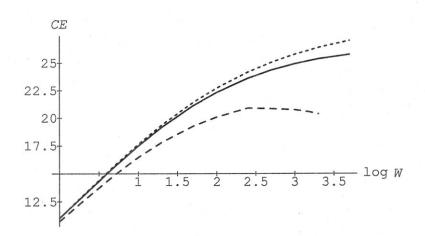

local storage and I/O costs, and the pebbling games address both these constraints. We will analyze the data dependency graphs of lattice-gas simulations using pebbling arguments to develop the required bounds on throughput. There are several issues that we address in this chapter that are essential to making performance comparisons. The first issue concerns the bounds established in previous work. In [21] and [23] the bounds are asymptotic in the amount of local processor storage. However, there are two problems with using these estimates: (1) although the bounds are valid within a finite range of values for the number of red pebbles used, the bounding arguments are not valid in the asymptotic limit, and (2) the valid portion of the resulting bounding curve is very loose. Thus, the primary task taken up here is to establish a sufficiently tight non-asymptotic bound using a variant of the red-blue pebble game.

The second issue we address is that making tighter bounds requires establishing a formal basis for these estimates. Previous work [24] attempting to establish tighter non-asymptotic bounds relied on two premises that were not established: (a) that the arrangement of r red pebbles in a data dependency graph that results in the largest amount of pebbling without I/O consists of placing all the pebbles in a single layer of the graph, and (b) that optimal arrangement within the layer consists of packing the vertices into a ball, the set of vertices with distance less than some parameter d from a specified vertex. The tasks taken up here then are the following:

- (1) Establish the formal basis for making size estimates of sets of data dependency graph nodes defined by pebbling. See section 2.2.

- (2) Solve the problem of extremal pebble sets, and derive the bounds on I/O costs. See section 2.3

- (3) Apply the I/O bounds to throughput comparisons. See section 2.4

Implicitly, there is another issue that is addressed here, at least partially. The shapes of sets of data dependency graph nodes defined by pebbling game optimization, define the computational strategy of least I/O cost. So, we hope to find not only the numerical value of the least I/O cost for a machine with given fixed machine resources, but also discover a method of determining the optimal computational strategy.

#### 2.2. The Formal Basis for Input/Output Bounds

#### 2.2.1. The Parallel Red-Blue Pebble Game

In this section we define the parallel-red-blue pebble game. It models any computation that can be performed by a machine which has arbitrary parallel I/O capabilities to an external memory, and internally is equivalent to a CRCW PRAM†. Before we discuss the necessity of defining a new pebbling game, we first need to review the definition of the original red-blue pebble game [21].

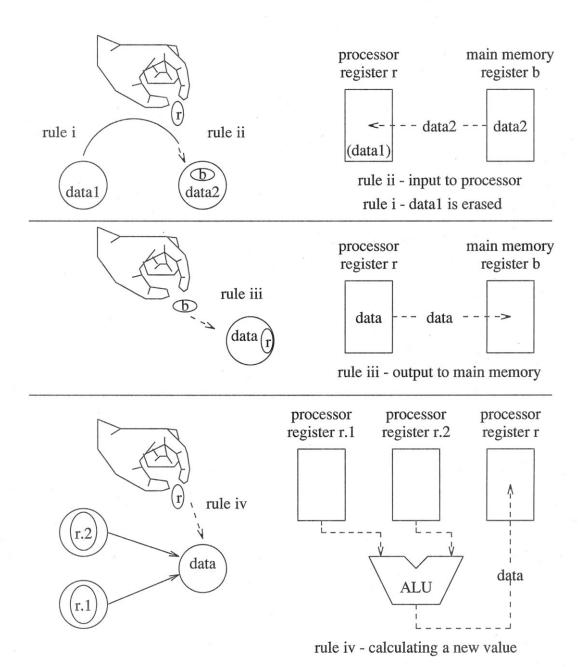

The red-blue pebble game is played on a directed acyclic graph with uniformly bounded indegree according the following rules (see figure 2.2).

- i) a pebble of any color may be removed from a vertex at any time.

- ii) a red pebble may be placed on any vertex that has a blue pebble.

- iii) a blue pebble may be placed on any vertex that has a red pebble.

- iv) if all immediate predecessors of a vertex v are red pebbled, v may be red pebbled.

The "inputs" are those vertices which have no predecessors, and the "outputs" are those which have no successors. A vertex that is blue-pebbled represents the associated value's presence in main memory. A red-pebbled vertex represents presence in processor (chip) memory. Rules (ii) and (iii) represent I/O, and Rule (iv) represents the computation of a new value. Generally, the game is played with a fixed number of red pebbles and an infinite supply of blue pebbles. The goal of the game is to blue-pebble the outputs given a starting configuration in which the inputs are blue-pebbled and the rest of the vertices are free of pebbles.

The need to add parallelism to the red-blue game is a consequence of the fact that it is an open question whether or not the red-blue game is sufficient for modelling I/O in general parallel computations. One approach to investing it with parallel properties without defining a new game consists of considering a block of moves as occurring in a single "time step". This allows a certain form of parallelism, and is the extension used by Savage and Vitter [22] in the block-red-blue game: the actual play of the game is not altered, but rather the counting of moves is redefined. However, in the general case, it is easy to find a simple example in which the number of I/O steps can be

<sup>†</sup> Such a machine model consists of an arbitrary number of processors communicating via a shared memory. This model is often referred to as a CRCW PRAM: concurrent-read concurrent-write parallel random access machine [26].

figure 2.2.

Interpretation of the rules of the standard red-blue pebble game. Rules i and ii are illustrated in the top diagram, Rule iii in the middle diagram, and Rule iv in the bottom diagram. Respectively, the interpretations are, register deallocation, write to processor register, write to main memory register, and write ALU result to local register. Ellipses labelled "r.1," "r.2," and "r" represent red pebbles, and those marked "b" represent blue pebbles.

reduced by allowing the Rule iv red pebbling moves to occur in parallel. The problem with the standard red-blue pebble game is that lifting a pebble to move it to a node that is being calculated may destroy the precondition for Rule iv red pebbling another node.

The parallelism we want to model in the red-blue game is to allow any number of pebble moves to occur simultaneously, so long as their preconditions allow a move in the non-parallel game, yet we also want to maintain a pebbling game that moves a single pebble at a time. The reason we want to maintain a linear ordering of pebble placement is that the method of bounding I/O cost depends on dividing any pebbling of a data dependency graph into pieces of equal I/O cost in such a way that the division induces a partition of the nodes of the graph into pieces whose sizes can be easily estimated. The size estimates on these pieces are derived from a bound on the maximum amount of pebbling possible given an arbitrary placement of red pebbles, but without the use of blue pebbles. Consequently, we must be sure that the partitioning does not violate the data dependencies; otherwise, an element of the partition might contain more nodes than the method of estimation allows, invalidating the estimate. If the pebbling moves are linearly ordered without data dependency violations, then the pebbling can be divided into contiguous pieces that result in a valid partitioning of the nodes. The red-blue pebble game can be so divided because it is a strictly sequential game: a single pebble is moved on the data dependency graph according to the rules stated above, and and the resulting configuration determines the applicable rules for the next move. Since we want to use the same techniques for bounding I/O cost in the parallel case as was used for the red-blue game, we want the parallel game to be a sequential game as well.

**Definition:** the rules of the parallel - red - blue pebble game:

The game is similar to the red-blue pebble game with the addition of a new pebble (pink, for "place holder"), and a modified Rule iv:

- i) a pebble of any color may be removed from a vertex at any time.

- ii) a red pebble may be placed on any vertex that has a blue pebble.

- iii) a blue pebble may be placed on any vertex that has a red pebble.

- iv) if all predecessors of a vertex v are pink pebbled, then v may be red pebbled.

- v) the game consists of cyclic repetition of three consecutive phases: writephase, calculate-phase, read-phase.

- vi) the write-phase consists of only Rule i and iii moves (output).

- vii) the calculate-phase comprises the following moves

- a) pink pebbles are placed on every node containing red pebbles

- b) red pebbles are moved according to Rules i and iv.

- c) at the end of the phase all pink pebbles are removed.

- viii) the read-phase consists of only Rule i and ii moves (input).

A complete cycle represents a single parallel step in the computation. We use the following terminology: placing a red pebble on a node that contains no red pebbles is a *calculation*. The node pebbled is called the *dependent* node, and the nodes with arcs ending at the dependent node are called the *supporting* nodes. Usually, the game is played with a restricted number of red pebbles.

It is easy to see the parallel-red-blue pebble game allows the parallelism we want. Consider a computation which proceeds by doing many steps in parallel in real time. Decompose the computation into pieces which occur simultaneously designated  $C_i$ ; we say complete computation Cconsists of their concatenation:  $C = C_1 \cdot C_2 \cdot \cdots \cdot C_k$ . Consider the pebble moves within a single parallel move  $C_i$ : memory reads, memory writes, and register to register calculations. Since all these actions take place simultaneously, we can order them arbitrarily because they are not interdependent. Thus, we may order them exactly as the phases are ordered in the parallel-red-blue game. Within the phases there are no interdependencies, and the individual moves may be arbitrarily ordered. Consequently, there is a pebbling that models the steps of the computation.

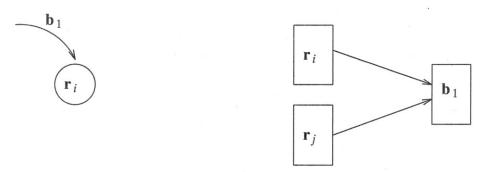

We next show that every pebbling represents a valid CRCW computation. Assume that every pebble move is valid, so far. The first phase of a cycle is the write-phase: some nodes with red pebbles on them get blue pebbles. The red pebbles were placed in an earlier cycle, so they are not a concern. A blue pebble that is moved onto a node containing a red pebble might have been sitting on another node previously; however, this simply represents a memory register overwrite of previously stored data, in the case that the blue pebble was not moved previously during this cycle, or it represents the concurrent writing of more than one register to the same memory location, in the case the blue pebble was moved in this cycle. Neither case conflicts with the model of computation. See figure 2.3.

The second phase is the calculate-phase: some nodes with all their supporting nodes pink-pebbled get one or more red pebbles. The sources for any calculation in

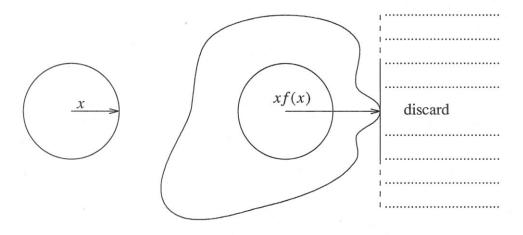

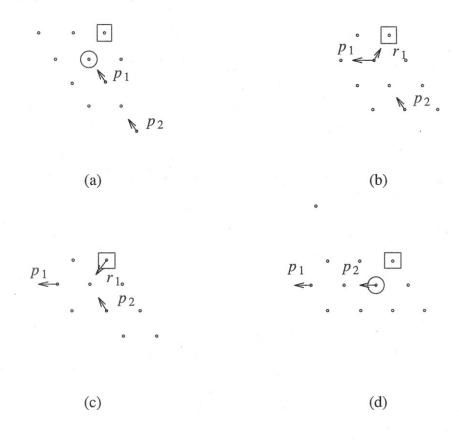

figure 2.3.

Left: A blue pebble,  $\mathbf{b}_1$ , is placed on a node of the data dependency graph that already has a red pebble  $\mathbf{r}_i$  on it. Right: the hardware interpretation is that the data held in register  $\mathbf{r}_i$  is written to the main memory register  $\mathbf{b}_1$ . If pebble  $\mathbf{b}_1$  is moved to another such node, say one containing pebble  $\mathbf{r}_j$ , the interpretation is that the two registers make concurrent writes to the same memory location; in this case the result is that the contents of  $\mathbf{r}_j$  end up in memory because the  $\mathbf{b}_1$  ends up on the same node as  $\mathbf{r}_j$ .

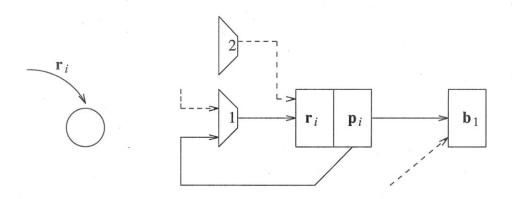

figure 2.4.

Left: a red pebble  $\mathbf{r}_i$  is placed on a node by using the calculation rule (the node may or may not have pebbles on it already). Right: the possible interactions are summarized. The output side of a master-slave register  $\mathbf{p}_i$  feeds into an ALU while the input side  $\mathbf{r}_i$  receives the result of the calculation. The red pebble  $\mathbf{r}_i$  may have been used in another calculation during this calculation-phase (indicated by dashed lines from ALU 2) which is interpreted as a concurrent write to register  $\mathbf{r}_i$ . The previous write-phase of the cycle also allows  $\mathbf{p}_i$  to concurrently fan-out its data to a memory location (that is, the pebble  $\mathbf{r}_i$  may have been moved from a node that was blue-pebbled in the write-phase).

this cycle, the supporting nodes, were red pebbled in a previous cycle (as opposed to having red pebbles during this cycle), so the input to the calculation is valid. There are two possible sources of conflict. The red pebble placed on the dependent node could have been on a node which was newly pebbled either blue or pink during this cycle. In

either case this represents simultaneously reading and writing the register associated with the red pebble. This is within the CRCW model, and is commonly implemented in practice. If the red pebble was used previously in this cycle to receive the results of a calculation, this is again a concurrent write to the same register; the "last write wins." See figure 2.4.

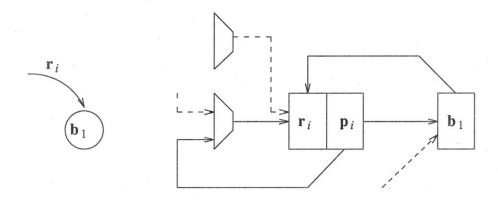

figure 2.5.

Left: a red pebble  $\mathbf{r}_i$  is placed on a node holding a blue pebble  $\mathbf{b}_1$ . Right: summarizing the result shows another concurrent write to register  $r_i$  (possibly from multiple memory locations).

The last phase is the read-phase: some blue pebbled nodes get red pebbles. There are again two possible conflicts: the red or blue pebbles may have been moved previously during this cycle. The blue pebble may have been used to receive data in the write-phase. Again this is concurrent reading and writing of a register. The red pebble may have been used as a data source for writing to memory, as a data source for a calculation, or as a destination for a calculation during this cycle. Again this represents concurrent read/write and again "last write wins." See figure 2.5.

#### 2.2.2. Dependency Graph Partitioning and Partition Element Estimators

This section sets forth the foundations of making input/output cost estimates (the "Partitioning Theorem", Theorem 1, and the "Dominator Theorem", Theorem 2). We use the general strategy introduced by Hong and Kung in [21] to get an estimate of the total input/output cost of an optimal pebbling using r red pebbles. Their strategy is as follows.

(1) Establish the existence of a partitioning of the nodes of a data-dependency graph G for any pebbling P of that graph using r red pebbles. The partition has the property that each element of the partition accounts for k I/O moves of P, where k is a

fixed constant parameter.

- (2) Find a bound  $\beta$  on the maximum number of elements in a member set of the partition.

- (a) Identify a convenient containing set for each element of the partition. The containing set is characterized by a "dominator" set of known size less than or equal to (r + k).

- (b) Establish an upper bound  $\beta(r, k)$  on the size of sets dominated by sets of size (r + k).

- (3) Estimate the number of sets in the partition as  $h \ge \frac{|G|}{\beta}$ . This gives a lower bound on the I/O cost as  $h \cdot k$ .

In the next section we address steps (1) and (2a). The method we use for (1) replaces the arguments based on paths in the data dependency graph used in [21] with careful definitions of vertex sets in pebbling games. The results are then simple consequences of the definitions, and allow precise identification of the sets for which we later develop size estimates. The method we use for (2a) significantly improves the estimate of maximum partition size so that the estimate is tighter.

We will need to develop some terminology which will allow us to precisely define the sets for which we want to develop size estimates. The appearance of the result may seem unnecessarily complicated; however, the need for such precision is demonstrated when subtle errors appear in arguments that do not use carefully defined terminology. For instance, in [14] the authors attempt to prove a result found in [21] concerning a lower bound on the total I/O of an FFT computation. The proof fails because of the mistaken identification of the sets of nodes red pebbled during I/O operations under different I/O conventions.

#### The Partitioning Theorem

This section develops notation for defining sets of vertices that arise implicitly in the play of the red-blue and parallel-red-blue pebble games. We begin with the definition of an I/O-division of a pebbling game, and conclude with a description of the induced partition of the nodes of the data dependency graph. In the following let a pebbling  $P = (p_1, p_2, \ldots, p_n)$ , where each of the  $p_i$  is a single pebbling move, be a pebbling of a computation graph G = (X, A), where X is the set of vertices of G and G is the set of directed edges in G. A sub-pebbling of G is any sub-sequence of consecutive pebbling moves of G. Let  $G_{I/O}$  be the number of G in G that are I/O moves.

Let k be a positive integer not greater than  $C_{I/O}$ , and define h as

$$h = \left\lceil \frac{C_{I/O}}{k} \right\rceil$$

, when  $C_{I/O} \neq 0$ , and otherwise  $h = 1$ .

**Definition:** A sequence of non-negative integers  $\sigma$  is a k-I/O-division of a pebbling if it satisfies the following:

- (i)  $\sigma = (\sigma_0, \sigma_1, \dots, \sigma_h)$  is a monotonically increasing sequence in the range [0, n] with  $\sigma_0 = 0$ , and  $\sigma_h = n$ .

- (ii)  $\sigma$  divides a pebbling P into h pieces ( $P_1, P_2, \ldots, P_h$ ) in the following sense:

Each of the pieces is a sub-pebbling of P:  $P_i \equiv (p_{\sigma_{i-1}+1}, p_{\sigma_{i-1}+2}, \dots, p_{\sigma_i}) \text{ for } 1 \le i \le h.$

Exactly k of the  $p_j$  contained in  $P_i$  are I/O moves, except that  $P_h$  may contain any integer number of I/O moves in the range [0, k]. (For instance, if there are k or fewer I/O moves in P, then  $\sigma = (0, n)$ , and  $P_h = P_1 = P$ .)

**Definition:** The Red Set at step i,  $R_i$ , is the sub-set of X containing the vertices which have red pebbles:

$$R_i = \{x \mid x \text{ has a red pebble after } p_i \}$$

.

П

Note that  $R_i - R_{i-1}$  identifies a vertex —if one exists— that was red-pebbled by pebbling move  $p_i$ . A pebbling begins with  $R_0 = \emptyset$ .

**Definition:** The *Blue Set at step* i,  $B_i$ , is defined analogously to  $R_i$ .

**Definition:** The Computed Set at step i,  $\Psi_i$ , is the sub-set of X that has been redpebbled at or before step i, or are inputs:

$$\Psi_i = \bigcup_{k=1}^i R_k + \Psi_0$$

where

$$\Psi_0 \equiv \{ x \mid x \text{ is an input vertex } \}$$

.

We interpret this set as the set of vertices that have been calculated up to the end of pebbling step i. (See figure 2.6.)

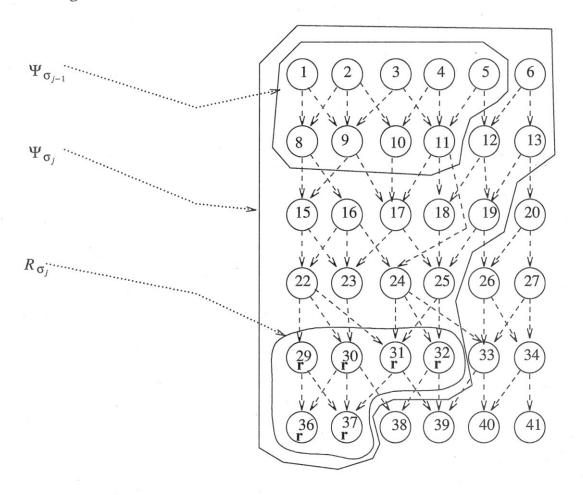

figure 2.6.

A pebbling game at the end of pebble step  $p_{\sigma_j}$ . (Note that nodes 7, 14, 21, and so on are not shown.)  $R_{\sigma_j}$  is the red-set at the end of move  $p_{\sigma_j}$ . The nodes in the region labelled  $\Psi_{\sigma_j}$  were red pebbled by some pebbling move  $p_i$  where  $1 \le i \le \sigma_j$ . Also,  $\Psi_{\sigma_j}$  indicates that the nodes  $\{20, 26, 27, 33, 34, 38-41\}$  were not red pebbled by any of these pebbling moves. The kernel is  $\hat{P}_j = \{12, 13, 15-19, 22-25, 29-32, 36, 37\}$ .

**Definition:** The *Kernel* of a sub-pebbling  $P_i$  is the set  $\hat{P}_i$  of vertices which get redpebbled for the first time by some move in  $P_i$ :

$$\hat{P}_i = \Psi_{\sigma_i} - \Psi_{\sigma_{i-1}}.$$

П

Note that  $\Psi_0$ , the set of inputs, is not contained in any kernel.

**Definition:** The *Red Closure* of a sub-pebbling  $P_i$  is the set  $\overline{P}_i^R$  of vertices that have been red-pebbled by some move in  $P_i$ :

$$\overline{P}_{i}^{R} = \bigcup_{j=(\sigma_{i-1}+1)}^{\sigma_{i}} (R_{j} - R_{j-1}).$$

In general,  $\hat{P}_i \neq \overline{P}_i^R$  since the red closure includes vertices which are red pebbled and already contain blue pebbles (input from main memory), and vertices which had been previously red-pebbled and were red-pebbled again during  $P_i$  (recalculation). The *Blue Closure* is defined analogously (see figure 2.7).

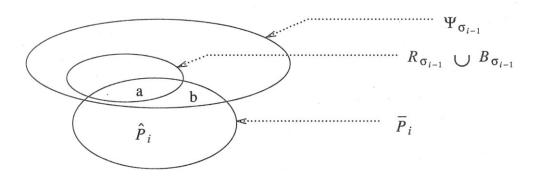

figure 2.7.

A Venn diagram of the sets defining the closure of a sub-pebbling. The region marked "a" indicates nodes that had red or blue pebbles on them at the start of sub-pebbling  $P_i$ , and were pebbled again in  $P_i$  (recalculation or I/O or both). The region marked "b" indicates nodes that had been calculated by previous sub-pebblings and were recalculated and possibly used for I/O in  $P_i$ .

**Definition:** The *Closure* of a sub-pebbling  $P_i$  is simply the set of vertices which were either red or blue pebbled during  $P_i$ :

$$\overline{P}_i = \overline{P}_i^B \bigcup \ \overline{P}_i^R \ .$$

We now state a partitioning theorem similar to the partitioning theorem in [21]. This theorem simply states that the kernels defined above partition the nodes of the data dependency graph.

**Theorem 1:** The collection of kernels of the sub-pebblings defined by a k-I/O-division,  $V = \{\hat{P}_1, \hat{P}_2, \ldots, \hat{P}_h\}$ , is a partition of the non-input vertices of the computation graph G = (X, A).

#### proof:

i) We assume throughout this chapter that the data dependency graphs do not contain useless nodes: nodes without incoming or outgoing arcs. Consequently, every vertex  $x \in X$  is red pebbled at least once, and therefore every vertex must belong to at least one red-set  $R_i$ :

$$\bigcup_{i=1}^{h} \hat{P}_{i} = \bigcup_{i=1}^{h} (\Psi_{\sigma_{i}} - \Psi_{\sigma_{i-1}})$$

$$= \bigcup_{i=1}^{h} (\bigcup_{j=1}^{\sigma_{i}} R_{j} - \bigcup_{j=1}^{\sigma_{i-1}} R_{j} - \Psi_{0})$$

$$= \bigcup_{i=1}^{h} (\bigcup_{j=\sigma_{i-1}}^{\sigma_{i}} R_{j}) - \Psi_{0}$$

$$= \bigcup_{j=1}^{n} R_{j} - \Psi_{0}$$

$$= X - \Psi_{0}.$$

ii) By definition the  $\hat{P}_i$  are all disjoint.

#### The Dominator Theorem

We now turn our attention from the sets defined by a pebbling, and define sets which are implied by the dependencies in G = (X, A).

**Definition:** The Support Neighborhood N(M) of a set  $M \subseteq X$  is the set of nodes which can be said to "support" the calculation of the nodes in M (see figure 2.8):

$$N(M) = \{ y \in X \mid (y, m) \text{ is an arc in } A \text{ and } m \in M \}.$$

$N^k(\ M\ )$  is the support neighborhood k levels back in the graph:

$$N^{k}(M) = N\left(N^{k-1}(M)\right)$$

, where

$$N^{0}(M) \equiv M$$

.

The Support  $\overline{N}(M)$  of a set is the union of all nodes necessary to calculate the set M:

$$\overline{N}(M) = \bigcup_{j=1}^{\infty} N^{j}(M) .$$

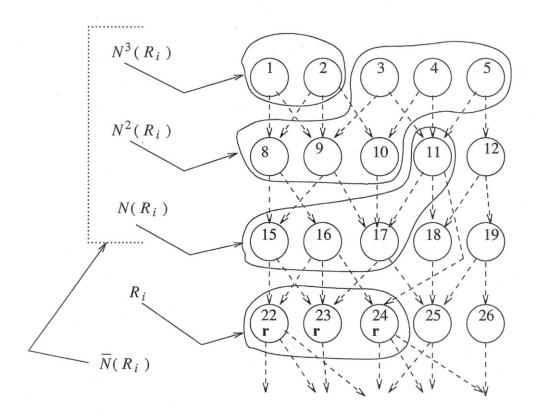

figure 2.8.

The support of the set  $R_i = \{22, 23, 24\}$ . The set  $\{1-5, 8-11, 15-17\}$  constitute the support of  $R_i$ : every node in this set must be pebbled before  $R_i$  can be completely pebbled.

**Definition:** The *Dependent Neighborhood* D(M) of a set  $M \subseteq X$  is the set of vertices which could be calculated by the next pebbling step if M was entirely red-pebbled but nodes outside of M were un-pebbled:

$$D(M) \,=\, \{x \mid \, N(x) \subseteq M\} \ - \ M \,.$$

The Dependency  $\overline{D}(M)$  of set M is the set containing all the vertices for which knowledge of M is sufficient for their computation:

$$\overline{D}(M) = \bigcup_{j=1}^{\infty} D^{j}(M)$$

where

$D^{k}(M)$  is the  $k^{th}$  recursive iteration of D(M), taking the union of previous neighborhoods to describe the next:

$$D^k(M) = D(M \cup \Theta_{k-1})$$

, where

$$\Theta_n = \bigcup_{j=1}^n D^j(M)$$

, and

$$\Theta_0 \equiv \emptyset$$

.

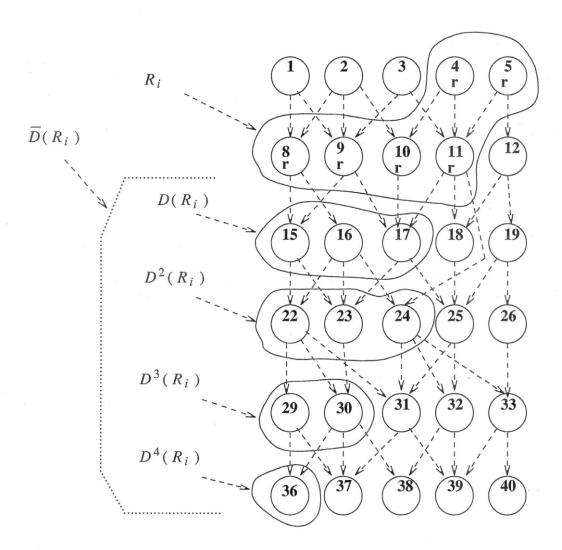

$\square$  Note that  $M \cap D^k(M) = \emptyset$  for all k. See figure 2.9.

As an aside, note that, given a set of nodes in a data dependency graph, it is intuitive that nodes that are not in its dependency cannot become a part of its dependency by addition of nodes and arcs to the graph. Establishing this allows the bounds on the sizes of dependencies to be

figure 2.9.

The dependency of the set  $R_i = \{4, 5, 8-10\}$ . The set of nodes  $\{15-17, 22-24, 29, 30, 36\}$  is the dependency of  $R_i$ : knowledge of the values in the nodes of  $R_i$  is sufficient to calculate all the nodes in its dependency.

applied to any super-graph. The statement of this proposition and its proof can be found in the appendix.

The estimates on the number of sets in a partition mentioned at the beginning of section 2.2.2 come from estimating the size of a convenient super-set: the dependency of some of the nodes containing pebbles before  $P_i$  begins. These pebbled nodes are called the *dominator* of  $P_i$ .

**Definition:** A set  $d_M$  is a *Dominator* of a set M, if

$$M \subseteq \overline{D}(d_M)$$

.

**Definition:** The Kernel Dominator,  $d_i$ , of the sub-pebbling  $P_i$  is

$$d_i = R_{\sigma_{i-1}} \cup (B_{\sigma_{i-1}} \cap \overline{P}_i^R) .$$

We will show below that  $d_i$  is in fact a dominator of  $\hat{P}_i$ . First we will show that the closure of  $P_i$  is contained in the union of  $d_i$  and the dependency of  $d_i$ .

### Lemma 1:

$$\overline{P}_i \subseteq (\overline{D}(d_i) \cup d_i).$$

## proof:

We use a straightforward induction to establish the above. In the following let  $P_i$  be a sub-pebbling with

$$P_i = (p_{\sigma_{i-1}+1}, p_{\sigma_{i-1}+2}, \cdots, p_{\sigma_i}).$$

For convenience, let us write

$$P_i = (p_1, p_2, ..., p_t)$$

,

where it is understood  $p_c$  represents  $p_{\sigma_{i-1}+c}$ , and that  $t \equiv \sigma_i - \sigma_{i-1}$ . Let  $Q_j$  be a sub-pebbling formed from  $P_i$  by taking the first j elements,

$$Q_j = (p_1, p_2, ..., p_j) \text{ for } 1 \le j \le t$$

.

The induction will be over j and we will show that the condition above is satisfied by  $\overline{Q}_j$ . Then, since  $\overline{P}_i = \overline{Q}_t$  we will have the result. Since the Rule i pebbling moves and any move of a pink pebble do not affect the definitions of the various node subsets, we will assume the moves in  $P_i$  consist only of moves placing a red or blue pebble on a node.

(basis):

$Q_1 = (p_1)$ . Let  $p_1$  pebble node x, then  $\overline{Q}_1 = \{x\}$ . There are three possible cases for  $p_1$ :

[1]  $p_1$  is a calculation. Then

$$N(x) \in R_{\sigma_{i-1}}$$

, and by definition  $x \in D^1(R_{\sigma_{i-1}}) \subseteq \overline{D}(d_i)$ .

[2]  $p_1$  is an input operation (adding red to blue on x). Then

$$x \in (B_{\sigma_{i-1}} \cap \overline{Q}_1^R) \subseteq d_i$$

, by

definition of  $\overline{P}_i^R$  and the definition of  $d_i$ .

[3]  $p_1$  is an output operation (adding blue to red on x). Then

$$x \in R_{\sigma_{i-1}} \subseteq d_i$$

.

(induction):

Assume  $\overline{Q}_k \subseteq (d_i \cup \overline{D}(d_i))$  for  $1 \le k < j$ . Now  $\overline{Q}_j = \{x\} \cup \overline{Q}_{j-1}$ , and we need only determine whether  $\{x\}$  is contained in  $(d_i \cup \overline{D}(d_i))$ .

[1]  $p_i$  is a calculation. Then

$$N(x) \subseteq (\overline{Q}_{j-1}^R \cup R_{\sigma_{i-1}})$$

, which implies that

$$N(x) \subseteq (\overline{D}(d_i) \cup d_i)$$

by the inductive hypothesis and

the definition of  $d_i$ , and consequently

$$x\,\in\,\overline{D}(\,d_i\,)\;.$$

[2]  $p_j$  is an input move. Then either

$$x \in B_{\sigma_{i-1}}$$

, in which case  $x \in (B_{\sigma_{i-1}} \cap \overline{Q}_j^R) \subseteq d_i$ , or  $x \in \overline{Q}_{j-1}^B$ , in which case  $x \in (R_{\sigma_{i-1}} \cup \overline{Q}_{j-1}^R) \subseteq (d_i \cup \overline{D}(d_i))$ .

The first instance follows from the definition of  $d_i$ ; and the second from the definition of  $d_i$ , the fact that  $\overline{Q}_{j-1}^R \subseteq \overline{Q}_{j-1}$ , and the inductive hypothesis.

[3]  $p_i$  is an output move. Then

$$x\in (R_{\sigma_{i-1}}\cup \overline{Q}_{j-1}^R)\subseteq (d_i\cup \overline{D}(d_i))$$

, which follows again from the definition of  $d_i$ , the fact that  $\overline{Q}_{j-1}^R\subseteq \overline{Q}_{j-1}$ , and the

inductive hypothesis.

**Theorem 2:** The set  $d_i$  is a dominator for  $\hat{P}_i$ .

**proof:** We want to show that  $\hat{P}_i \subseteq \overline{D}(d_i)$ . Using the previous lemma and the definition of a kernel gives us

$$\hat{P}_i \subseteq (d_i \cup \overline{D}(d_i)) .$$

We need only to establish that  $\hat{P}_i \cap d_i = \emptyset$ , which follows immediately from

$$\hat{P}_i \cap (R_{\sigma_{i-1}} \cup B_{\sigma_{i-1}}) = \emptyset$$

and

the definition of  $d_i$ .

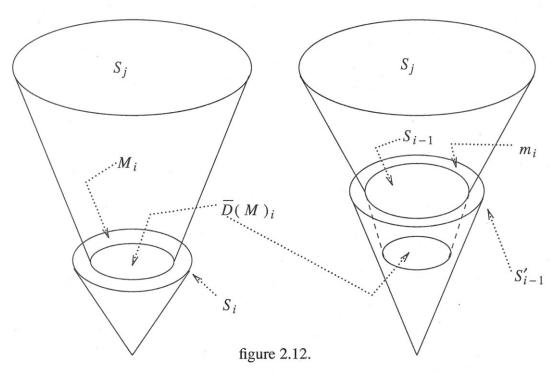

### 2.3. The I/O Bound from the Maximum Kernel Size

A data dependency graph can be pebbled in many ways. The optimal pebbling, from an I/O cost standpoint, makes the fewest I/O pebble moves. While we cannot find the optimal pebbling strategy for an arbitrary lattice-graph computation, we can at least lower bound its I/O cost. The bound comes from an upper bound on the size of a subpebbling kernel. That is, since almost every sub-pebbling in a k-I/O-division contains exactly k I/O moves, and the kernels partition the nodes of the data dependency graph, dividing the number of nodes by the maximum size of a kernel leads to the desired bound on I/O cost.

Let P be a pebbling of a computation graph G = (X, A) with input vertex set  $I^G \subseteq X$  where the number of non-input vertices in G is  $z = |X - I^G|$ . For any k a k-I/O-division divides P into h(k) pieces,  $\{P_1, \ldots, P_{h(k)}\}$ . The I/O cost,  $C_{I/O}$ , of pebbling P is given by

$$C_{I/O} = (h-1) k + \varepsilon(k)$$

,  $\varepsilon(k) \in [0, k]$  where

the last sub-pebbling has  $\varepsilon(k)$  I/O moves. Suppose we have a lower bound  $\hat{h}$  for h, then the I/O cost is bounded below:

$$C_{I/O} \geq (\hat{h}(k) - 1) k$$

.

Bounding h can be done by finding some upper limit  $\beta$  on the size of a sub-pebbling kernel,  $\hat{P}_i$ . Then, because Theorem 1 tells us that  $\{\hat{P}_i\}$  partitions  $X - I^G$ ,

$$z = |X - I^G| = \sum_{i=1}^h |\hat{P}_i| \leq h \beta,$$

and the desired bound for h is

$$\hat{h} = \frac{z}{\beta}$$

.

The bound for the I/O cost of P becomes

$$C_{I/O} \geq \left[\frac{z}{\beta} - 1\right] k$$

.

By Theorem 2,  $\hat{P}_i \subseteq \overline{D}(d_i)$ , and the size of each kernel is bounded above by  $|\overline{D}(d_i)|$ . A suitable choice for  $\beta$  then is  $\beta = \max |\overline{D}(d_i)|$  where the maximum is taken over all pebblings using at most r red pebbles. In general,  $\beta$  is a function,  $\beta = \beta(r, k)$ , of the number of red pebbles used by P,  $r = \max_i |R_i|$ , and k, the number of I/O moves per element of the k-I/O-division. The rest of this section develops bounds on  $\beta$

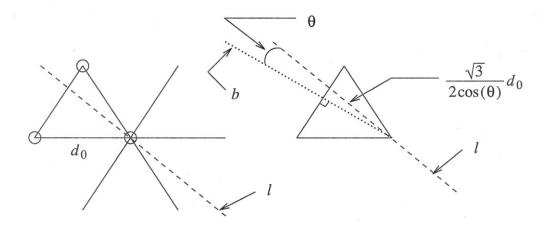

In particular, the following subsections present a method of estimating the maximum size of the dependency of a set. Section 2.3.1 establishes the the necessary basis for assuming the dependency takes a general shape, the "Symmetrization Theorem", Theorem 3, and the "One Level Theorem", Theorem 4. Section 2.3.2 finds the particular shape and size for the discrete torus, and Section 2.3.3 does the same for the triangular lattice.

### 2.3.1. Bounding the Size of the Dependency of a Set

The previous section established the basis for making I/O estimates based on pebblings. In particular, a suitable estimate comes from bounding the maximum size of the dependencies of a special collection of sets, the kernel dominators. The bound on the maximum size of such a dependency is derived from (1) bounding the size of the dominator by some value m, and (2) deriving a tight isoperimetric inequality for  $|\overline{D}(M)|$  for sets M with |M| = m. This isoperimetric problem is

(ISO-1)

Given a computation graph G and  $m \in \mathbb{Z}_+$ , find a function f such that

$$f(m) \geq |\overline{D}(M)|$$

for any subset M of the vertices of G where |M| = m. (The symbol  $Z_+$  represents the non-negative integers  $= \{0, 1, 2, \dots \}$ .)

A simple estimate can be made for part (1), and we leave it for later. Part (2) requires finding the shape of at least one extremal set  $\overline{D}(M)$  for each value of m, and that problem is addressed in two parts: (a) we show that for every extremal set  $\overline{D}(M)$  there is another extremal set which is a symmetrized version of  $\overline{D}(M)$ , and (b), we show that for any symmetrized extremal set there is another extremal set with the vertices of M compacted together into a special form. This special form will allow us to find an f such that  $f(m) = |\overline{D}(M)|$  for any extremal set for (ISO-1) with |M| = m.

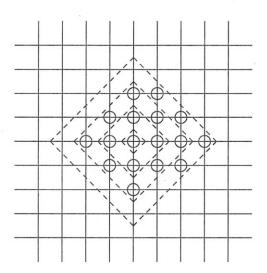

Although the results in the previous section apply to general data dependency graphs, in order to get these results we will restrict our attention in (a) to graphs that represent "lattice-graph computations" with the "nested" property, and in (b) add the further restriction to computations on the discrete torus. The types of data dependency graphs we will define as "lattice-graph computations" are layered directed graphs. In cellular automata, and particularly lattice-gas automata, values are associated with lattice points in an undirected lattice graph (see [1] for the precise definition of lattice graphs) and these values are updated in synchronous steps. Similar conditions also hold for many other iterated computations whose computation graphs may not be layered in the strict sense, but still have a structure similar to layering in that there is some connected undirected graph implicitly defined that can be used to define a layered subgraph. Theorem 2 in the previous section allows us to apply results for a graph to any of its supergraphs as well; consequently, we need only consider strictly layered graphs.

### **Dependency Set Symmetrization**

This section will show that an extremal  $\overline{D}(M)$  can be transformed to another extremal set whose layers are extremal sets in the undirected graph defining the data dependencies. We will rely heavily on recent results by Bollobás and Leader [27, 28] for extremal sets in undirected graphs, and our notation will attempt to conform to theirs whenever possible. In the following let L = (V, E) be an undirected graph with vertex set V and edge set E.

**Definition:** The *Distance* d(x, y) between a pair of vertices in an undirected graph G = (V, E) is the number of edges in the shortest path connecting x and y. A vertex is connected to itself and  $d(x, x) \equiv 0$ .

**Definition:** The *Neighborhood*,  $\Lambda M$ , of a vertex subset  $M \subseteq V$  is the set of vertices at most unit distance from M

$$\Lambda M = \{ v \in V \mid d(v, m) \leq 1, m \in M \}$$

, and

$$\Lambda^k \equiv \Lambda(\Lambda^{k-1}) .$$

**Definition:** The *External Perimeter*,  $\partial_{ex}M$ , of M is the set of vertices at unit distance from M:

$$\partial_{ex} M = \Lambda M - M$$

.

The Internal Perimeter,  $\partial_{in}M$ , is the subset of M adjacent to M's external perimeter:

$$\partial_{in}M = \Lambda M^c - M^c$$

, where

$M^c$  is the set complement of M with respect to the set of vertices V:  $M^c = V - M$ .

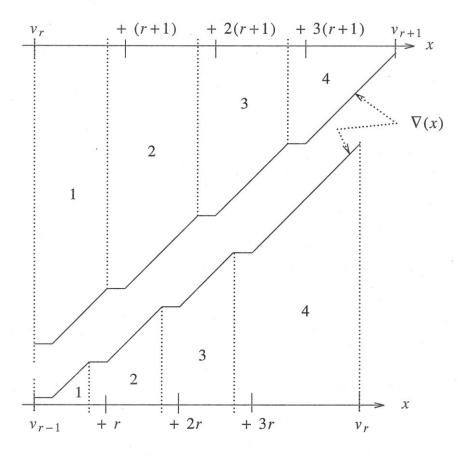

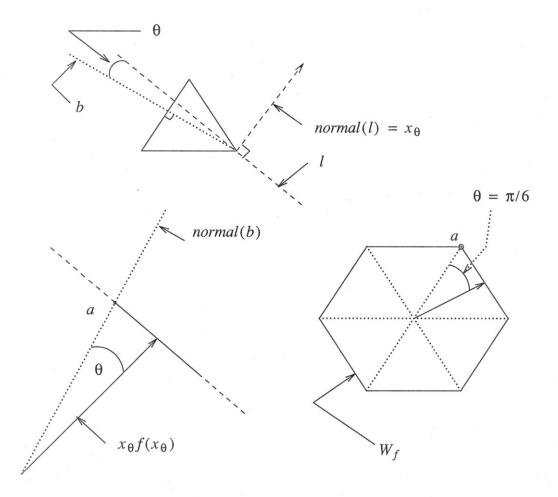

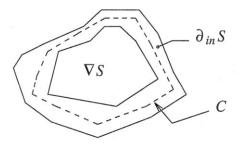

The *Interior*,  $\nabla M$ , is the subset of M which has no neighbors outside of M:

$$\nabla M = M - \partial_{in} M .$$

See figure 2.10. Equivalently, one can say that a vertex x is in the interior of M if  $\Lambda x \subseteq M$ .

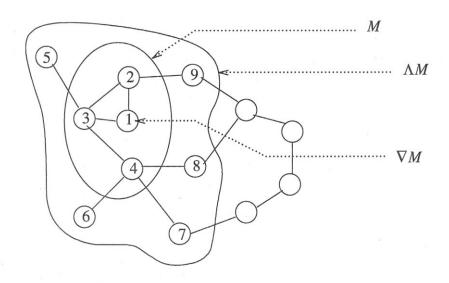

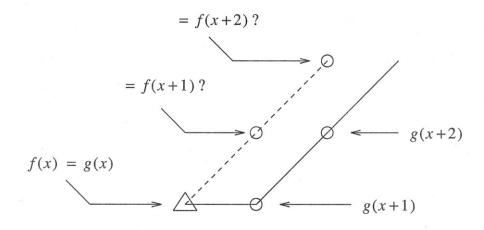

figure 2.10.

Sets defined in an undirected graph by a subset of the vertices  $M = \{1, 2, 3, 4\}$ . The interior is  $\nabla M = \{1\}$ , the internal perimeter is  $\partial_{in}M = \{2, 3, 4\}$ , the external perimeter is  $\partial_{ex}M = \{5, 6, 7, 8, 9\}$ , and the neighborhood is  $\Delta M = \{1-9\}$ .

To clarify the relationships between these set operators, note first that, generally  $\Lambda$  is not a left inverse of  $\nabla$ . That is,  $\Lambda \nabla M$  may be a proper subset of M. Another way of

saying the same thing is to say that  $\partial_{ex} \nabla M$  may be a proper subset of  $\partial_{in} M$ .

Let G = (X, A), be a data dependency graph for some computation. Let the inputs of G, those vertices in X with in-degree zero, be  $I^G$ . Recall that  $D^i(M)$  is the subset of X that is the  $i^{th}$  iteration of the dependency operator D operating on M. Thus,  $D^i(I^G)$  is the set of vertices at the  $i^{th}$  level of a breadth-first search from the input vertices of G.

**Definition:** The  $i^{th}$  Layer of G is

$$G_i = D^i(I^G)$$

, where

we define  $G_0 \equiv I^G$ . We say that G has k layers if k is the least i such that  $D^i(I^G) = \emptyset$ .

**Definition:** The Sections  $S_i$  of a set S, where S is a subset of the vertices of a computation G, are the subsets of S contained in the layers of G:

$$S_i \equiv S \cap G_i$$

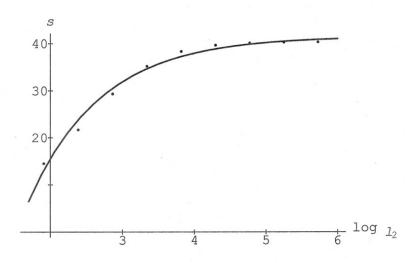

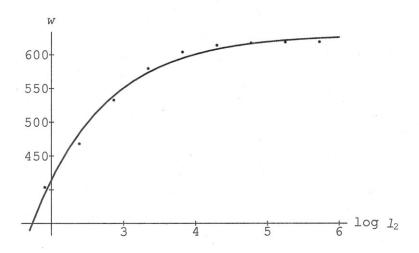

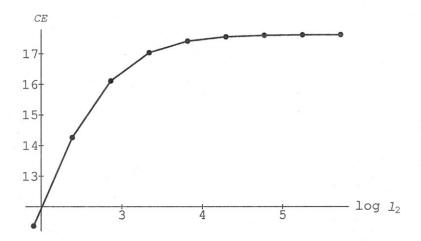

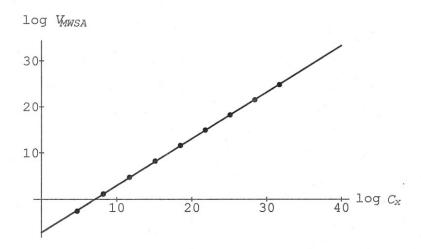

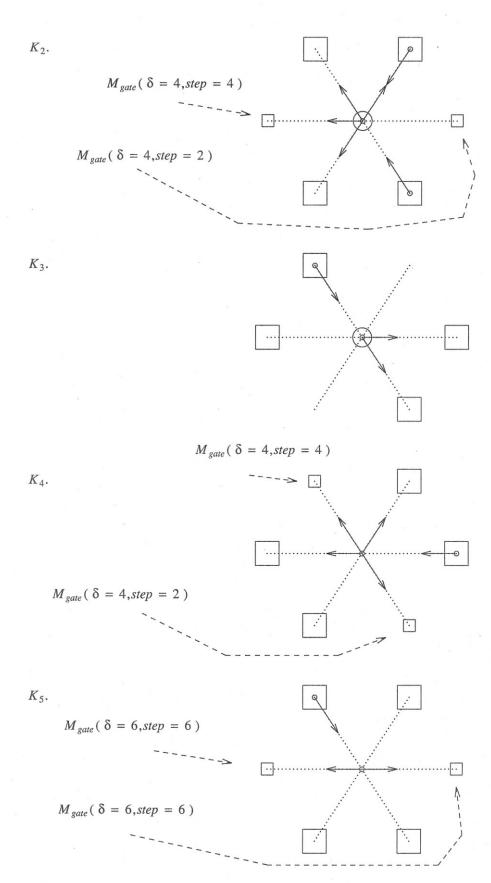

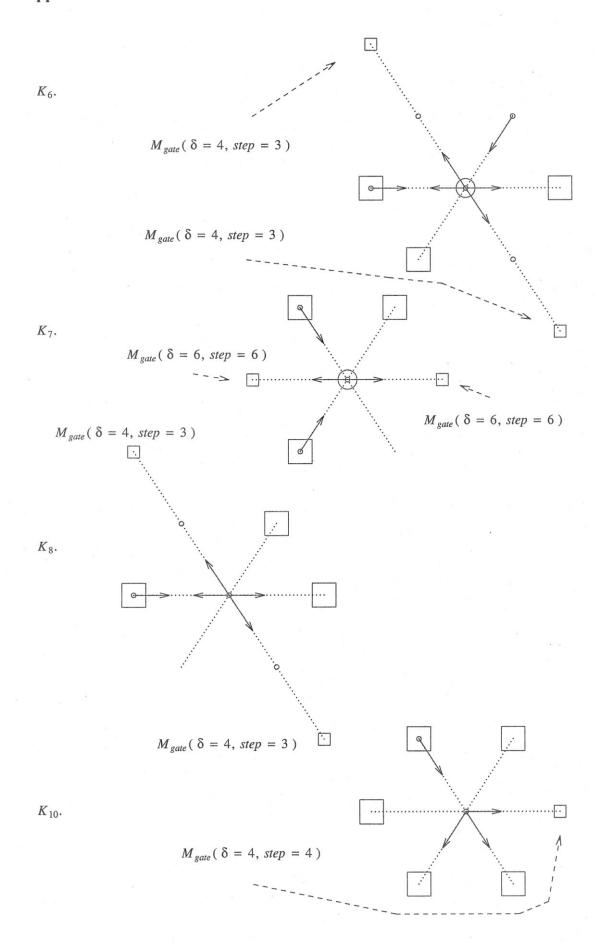

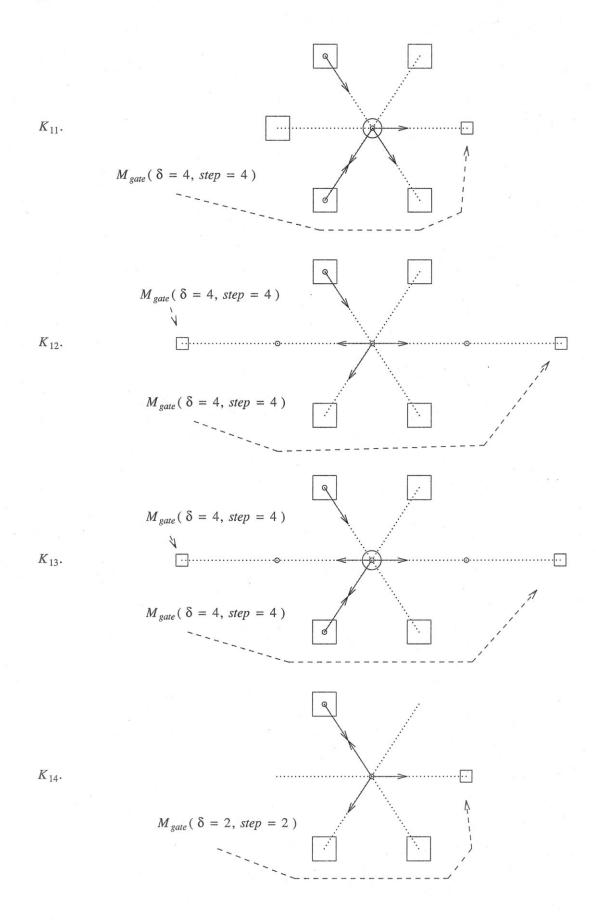

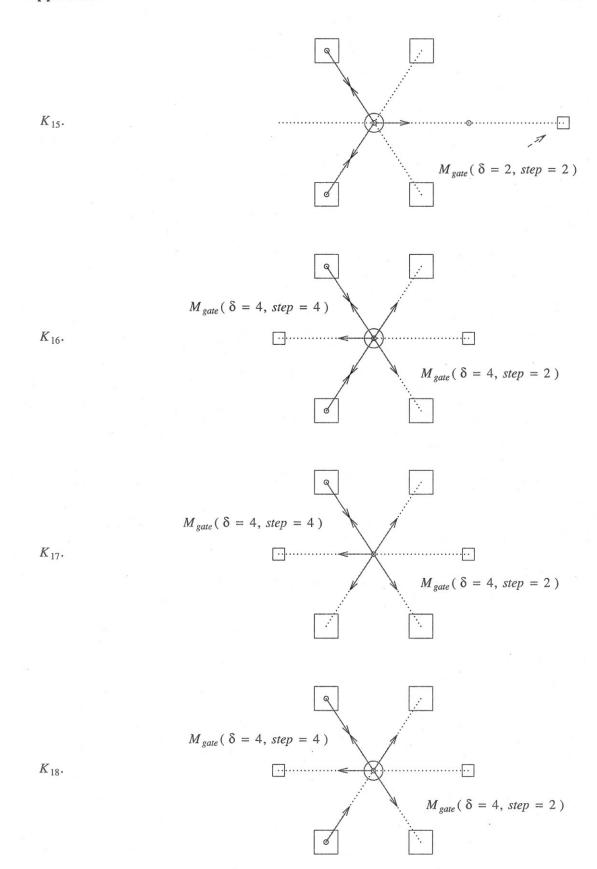

.