# ARCHITECTURES FOR TWO-DIMENSIONAL LATTICE COMPUTATIONS WITH LINEAR SPEEDUP

Steven D. Kugelmass (Thesis)

CS-TR-156-88

June 1988

## Architectures for Two-Dimensional Lattice Computations with Linear Speedup

Steven D. Kugelmass

A Dissertation

Presented to the

Faculty of Princeton University

In Candidacy for the Degree

of Doctor of Philosophy

Recommended for Acceptance by the Department of Computer Science

©1988 Steven D. Kugelmass All Rights Reserved

#### Abstract

Many problems are characterized by the fact that they deal with data values distributed on a regular mesh, or *lattice*. They arise in a wide variety of applications such as image processing, computer vision, the solution of partial differential equations, and the simulation of cellular automata. This dissertation explores theoretical and practical questions in the design of massively parallel machines for lattice processing.

We analyze and compare two architectures that are efficient for lattice computations and are suitable for VLSI implementation: the linear array, and a block partitioned architecture proposed by Sternberg. These architectures have a property called *linear speedup*. That is, n processors of fixed size and cost provide n times the throughput of one processor on the same problem instance. We find that the linear pipelined array is the more attractive of the two architectures for a two-dimensional lattice machine, because of its great simplicity.

We next study the effect of clock skew as a possible limitation on the ultimate performance of large, globally synchronized multi-processing systems. We propose and analyze a probabilistic model for clock skew accumulation based on variations in buffer and wire delays. Our main result is that the expected skew grows as  $O(\log N)$  in a system with N buffers, each of which contributes an independent, zero-mean, Gaussian skew. We also derive bounds on expected total clock skew when the skew in each stage depends on wire length, and the distribution system is embedded in the plane.

The remainder of this dissertation describes the design and construction of a prototype machine, called LGM-1 (for Lattice Gas Machine), for simulating the Frisch-Hasslacher-Pomeau (FHP) latticegas model for fluid flow. It consists of a one-dimensional pipeline of ten identical full-custom chips hosted by a Sun 3/160C workstation. The 64-pin DIP chips were fabricated by MOSIS in 3µ CMOS, and each contains more than 65,000 transistors. The chips themselves are capable of 14 million site-updates/sec/chip. The particular workstation host and interface limit the performance of LGM-1 to 7 million site-updates/sec, which is nevertheless about 60 times faster than a software simulation on the DEC VAX 8650.

for Ariela

#### Acknowledgements

I extend my deepest gratitude to my advisor, Professor Kenneth Steiglitz, who accepted me as his apprentice for the last three years. This work would not have possible without his support, and the quality would have suffered without his critical eye.

Professors Kai Li and Rafael Alonso are thanked for their critical and thorough reading of this dissertation. MOSIS provided the fabrication service for the VLSI chips for which I am also indebted.

One can never thank one's parents and family enough for the love, guidance, encouragement and support that they give. They have always encouraged me to achieve the most that I can and to never stop trying.

Ariela, my wife, has been my light, my partner and my friend. It is to her that this dissertation is lovingly dedicated.

### **Table of Contents**

| Abstract                                                  | ii  |  |  |

|-----------------------------------------------------------|-----|--|--|

| Acknowledgements                                          |     |  |  |

| Table of Contents                                         |     |  |  |

| List of Figures and Tables                                | vii |  |  |

| Chapter 1 Introduction and Background                     | , 1 |  |  |

| 1.1 History                                               | . 1 |  |  |

| 1.2 The FHP Lattice Gas Model                             | 2   |  |  |

| 1.3 Scattering Rules                                      | 2   |  |  |

| 1.4 Summary of Results                                    | 8   |  |  |

| 1.5 Previously Published Material                         | 9   |  |  |

| Chapter 2 Analysis of Lattice Architectures               | 10  |  |  |

| 2.1 Introduction                                          |     |  |  |

| 2.2 A Paradigm For Lattice Computations                   | 11  |  |  |

| 2.3 Serial Pipelined Architectures for Lattice Processing | 12  |  |  |

| 2.4 Wide Serial Architecture                              | 14  |  |  |

| 2.5 Sternberg Partitioned Architecture                    | 14  |  |  |

| 2.6 Analysis and Comparison of WSA and SPA                | 15  |  |  |

|                                                           |     |  |  |

| 2.7 Wide Serial Architecture                              | 17  |  |  |

| 2.8 Sternberg Partitioned Architecture                    | 20  |  |  |

| 2.9 Discussion                                            |     |  |  |

| 2.10 Summary                                              | 23  |  |  |

| Chapter 3 A Probabilistic Model For Clock Skew            |     |  |  |

| 3.1 Introduction                                          | 24  |  |  |

| 3.2 A General Model of Signal Distribution                |     |  |  |

| 3.3 Analysis and Upper Bounds                             | 26  |  |  |

| 3.4 Examples                                              | 30  |  |  |

| 3.5 Metric-Free Tree                                      | 30  |  |  |

| 3.6 Metric Tree                                           | 33  |  |  |

| 3.7 Discussion                                            |     |  |  |

| 3.8 Conclusions                                           |     |  |  |

| 3.9 Acknowledgements                                      | 35  |  |  |

| Chapter 4 Lattice Gas Cellular Automaton CMOS Chip        | 36  |  |  |

| 4.1 Introduction                                          |     |  |  |

| 4.2 The Lattice and Data Encoding                         | 37  |  |  |

| 4.3 Raster Scan                                           | 40  |  |  |

| 4.4 Architecture and Organization Overview                | 41  |  |  |

| 4.5 Hardware Implementation                               | 43  |  |  |

| 4.6 Shift Registers                                       | 44  |  |  |

| 4.7 Neighborhood Generator                                | 45  |  |  |

| 4.8 Update Processors                                     | 43  |  |  |

| 4.0 Testing Circuitry                                     |     |  |  |

| 4.9 Testing Circuitry                                     | 47  |  |  |

| 4.10 Miscellany                                           | 48  |  |  |

| 4.11 Testing and Performance                              | 48  |  |  |

| 4.12 Comparison to Other Machines                         | 49  |  |  |

| Chapter  | 5 LGM-1, A Prototype Lattice Gas Machine                                    | 50 |

|----------|-----------------------------------------------------------------------------|----|

|          | Overview                                                                    | 50 |

|          | Hardware                                                                    | 51 |

|          | Implementation Overview                                                     | 52 |

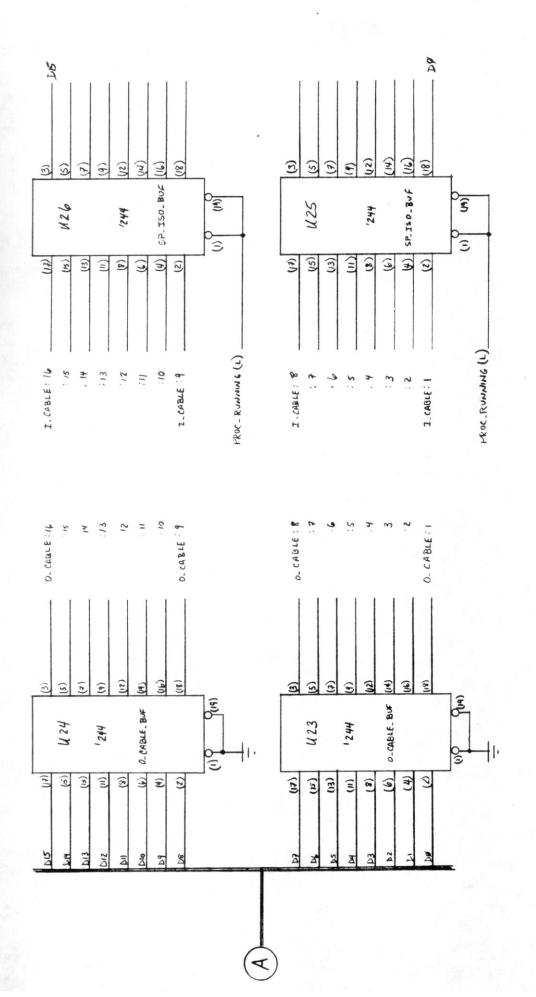

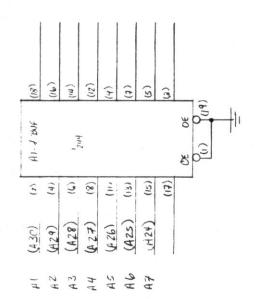

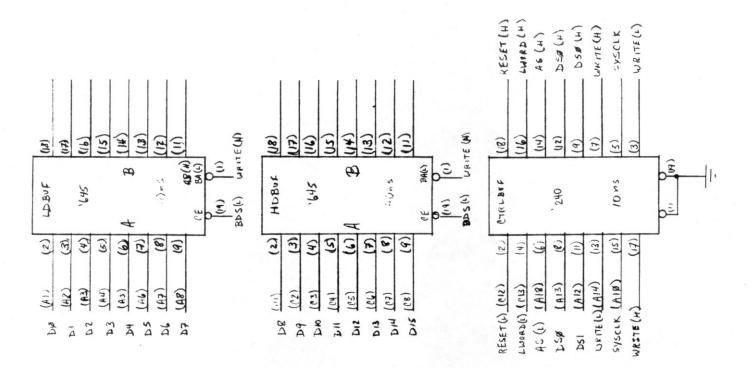

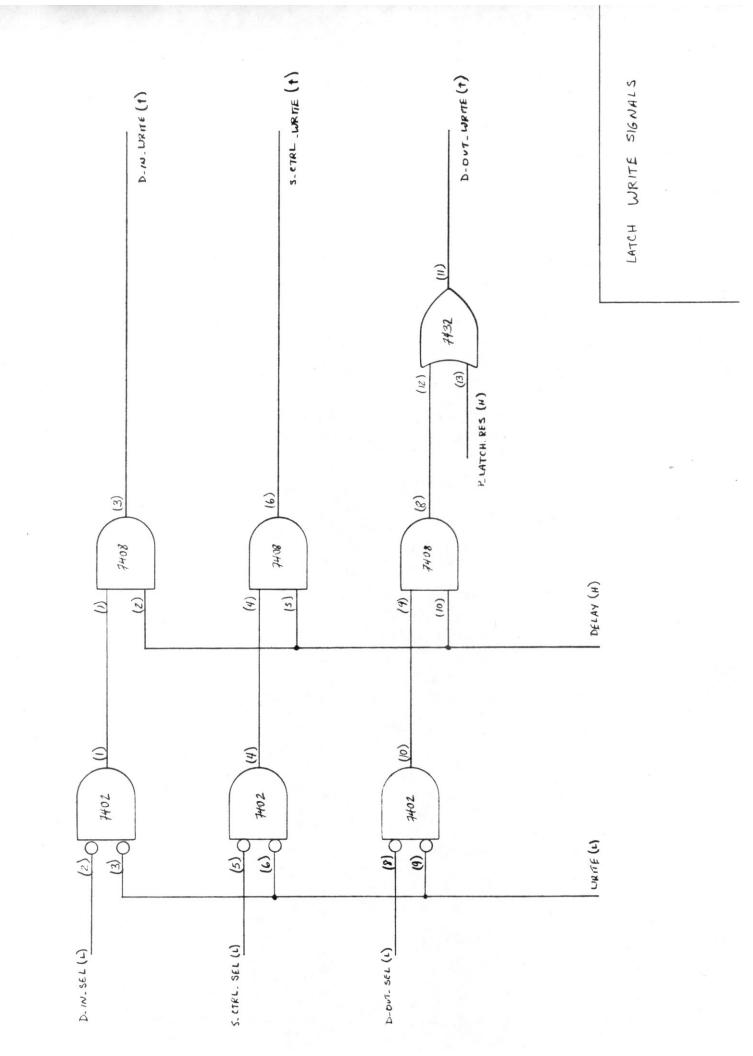

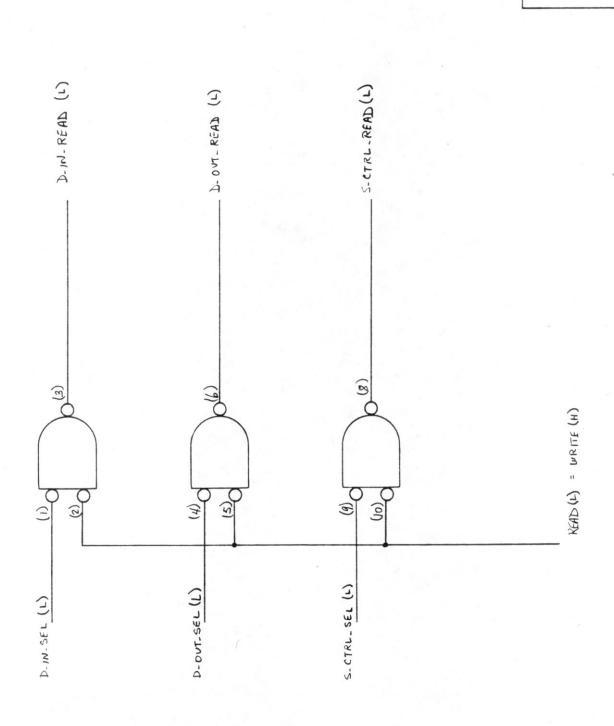

|          | Data Path                                                                   | 52 |

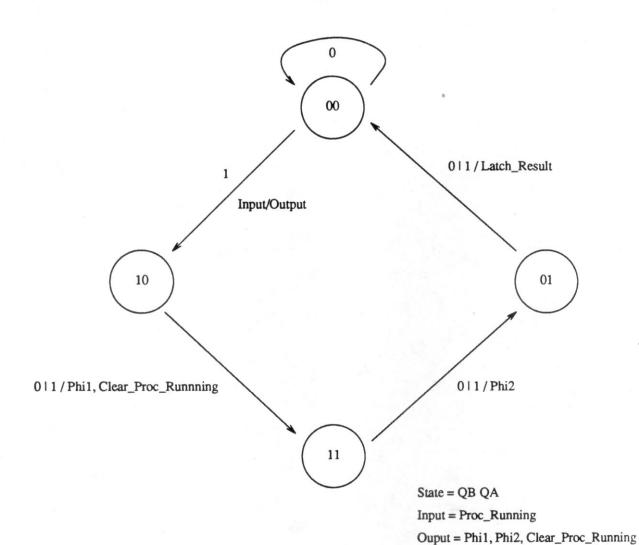

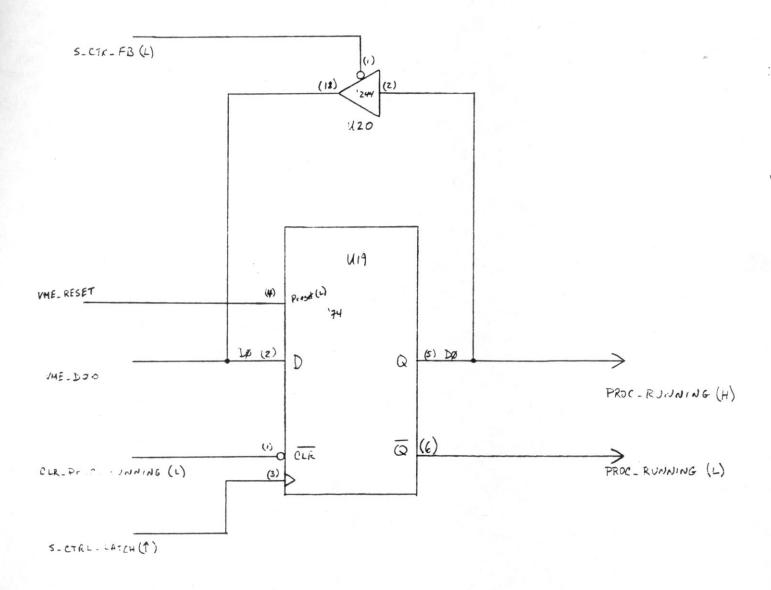

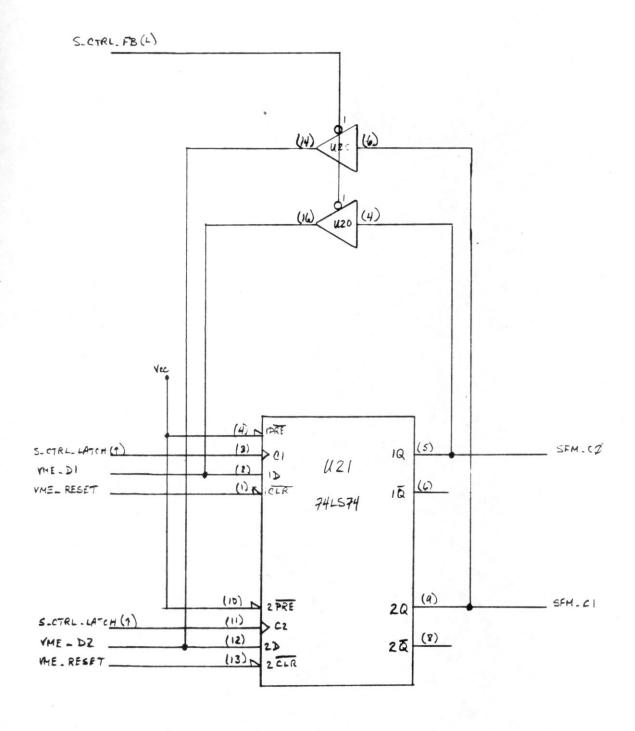

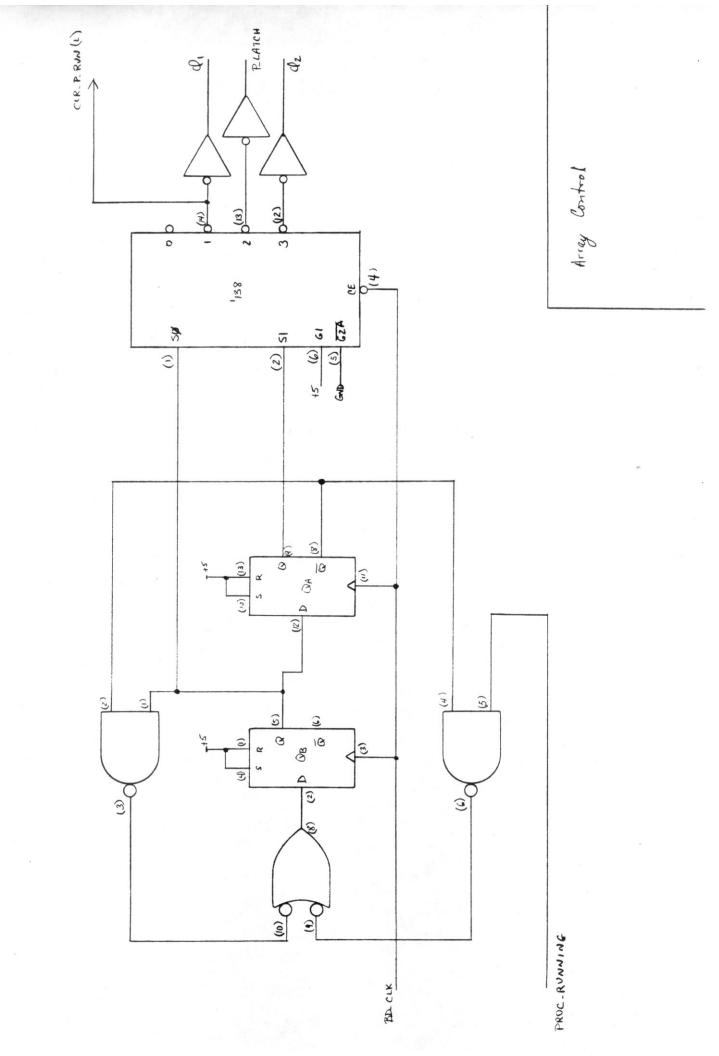

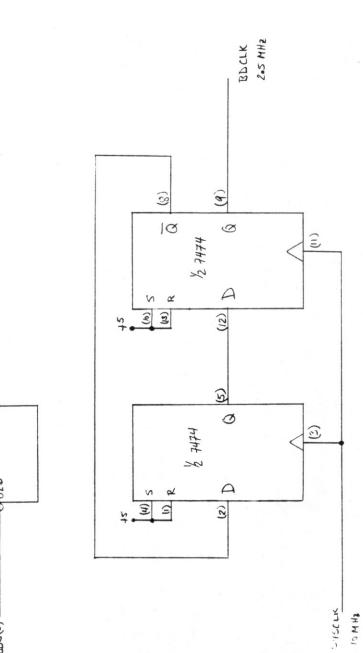

|          | Control Path                                                                | 52 |

|          | Programming Model                                                           | 53 |

|          | Graphic Display                                                             | 55 |

|          | Performance Levels of Current System                                        | 55 |

| Chapter  | 6 A Proposed Environment For Fast Prototyping of Linear Systolic Processors | 67 |

| 6.1      | Overview                                                                    | 67 |

|          | Hardware Specification                                                      | 70 |

|          | Software Specification                                                      | 71 |

|          | Physical Specification                                                      | 71 |

|          | Final Comments                                                              | 72 |

| Chapter  | 7 Conclusions and Future Work                                               | 74 |

| 7.1      | Summary and Conclusions                                                     | 74 |

|          | Next Steps                                                                  | 76 |

| Bibliogr | aphy                                                                        | 78 |

| Annendi  | v 1                                                                         | 81 |

## List of Figures and Tables

| Figure 1-1  | Single site with links numbered              | 3  |

|-------------|----------------------------------------------|----|

| Figure 1-2  | The hexagonal lattice                        | 4  |

| Figure 1-3  | Particle collision rule classes              | 5  |

| Figure 1-4  | Torroidal Lattice                            | 7  |

| Figure 2-1  | One-dimensional pipeline                     | 12 |

| Figure 2-2  | Hexagonal neighborhood                       | 13 |

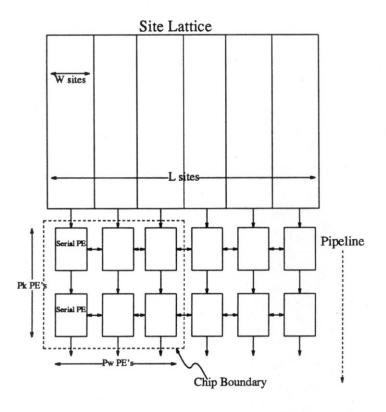

| Figure 2-3  | Wide serial architecture                     | 15 |

| Figure 2-4  | Sternberg partitioned architecture           | 16 |

| Figure 3-1  | Clock distribution tree                      | 30 |

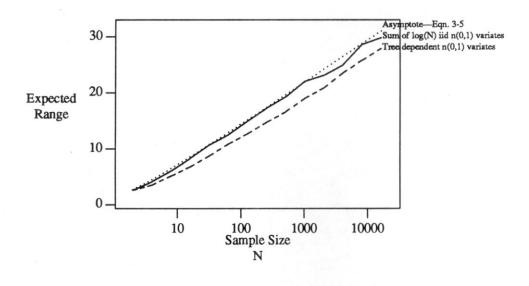

| Figure 3-2  | Range/Skew of Random Variables (Metric Free) | 32 |

| Figure 3-3  | Skew in tree with uniform and gaussian delay | 32 |

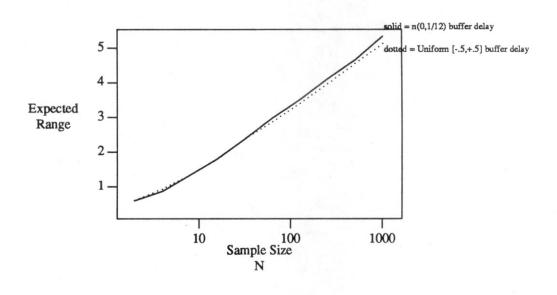

| Figure 3-4  | Range/Skew of Random Variables (Metric)      | 34 |

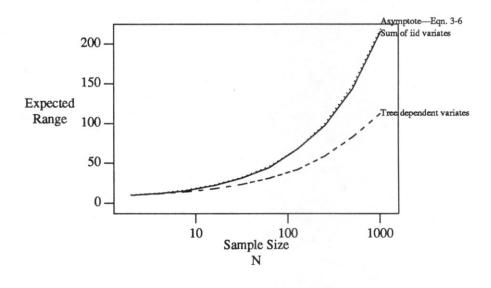

| Figure 4-1  | Space/Time Diagram of Pipelined Computation  | 37 |

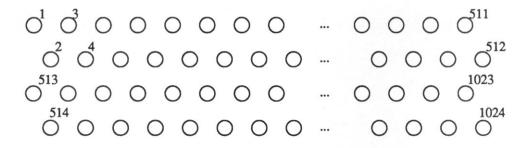

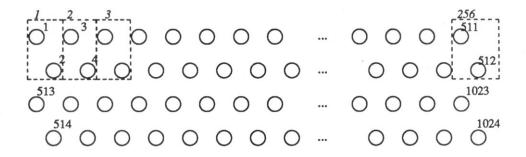

| Figure 4-2  | Theoretical and Implemented Lattices         | 38 |

| Figure 4-3  | Site state encoding                          | 39 |

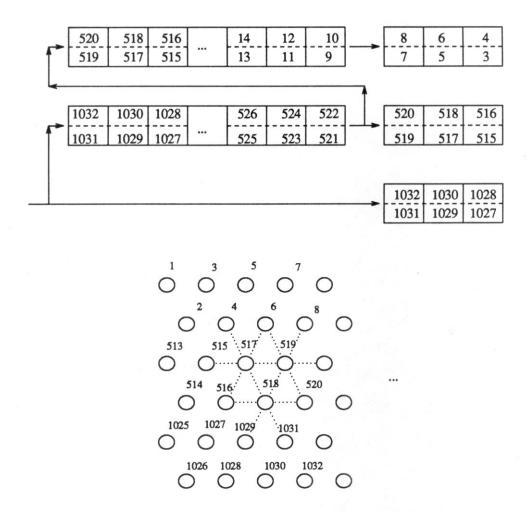

| Figure 4-4  | Lattice Site Numbering                       | 40 |

| Figure 4-5  | Raster Scan Pattern                          | 41 |

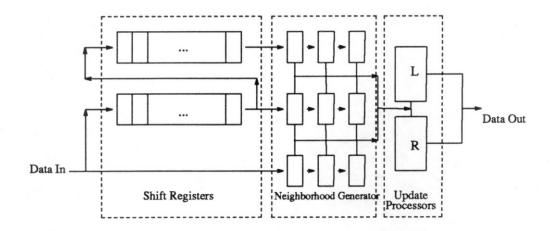

| Figure 4-6  | Basic Architectural Plan                     | 42 |

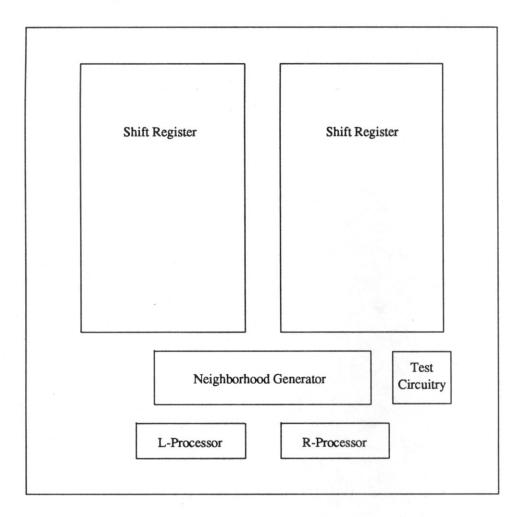

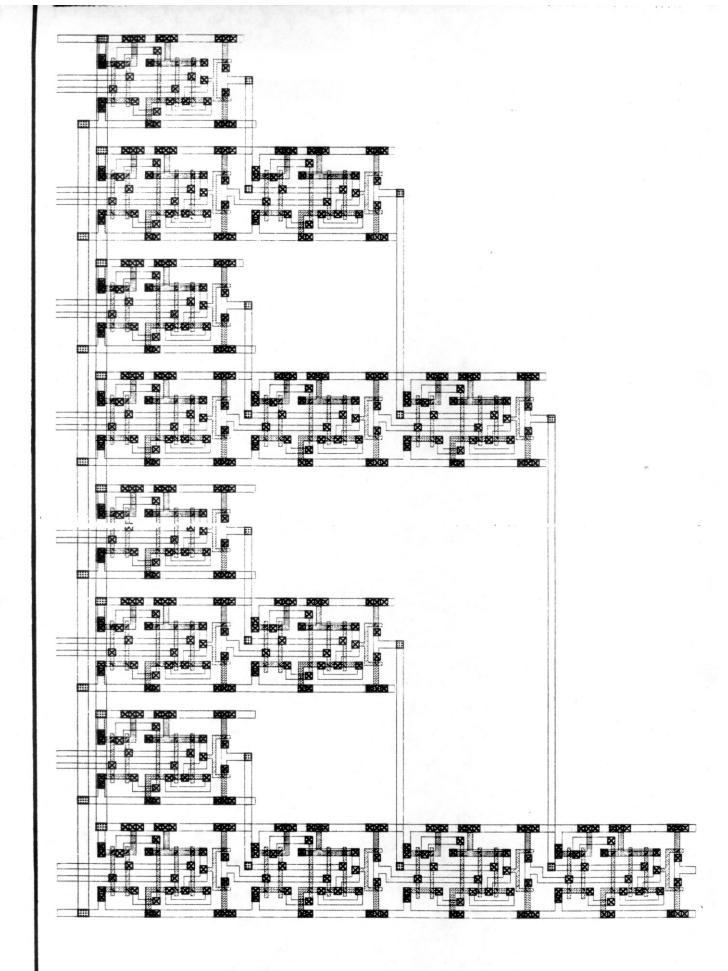

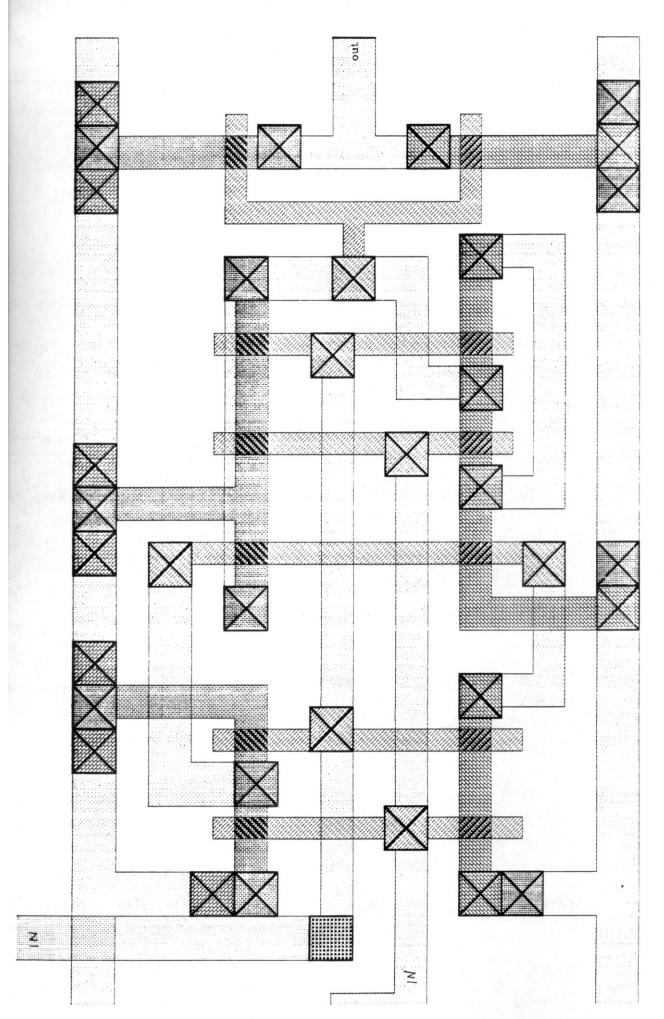

| Figure 4-7  | Chip Floor Plan                              | 44 |

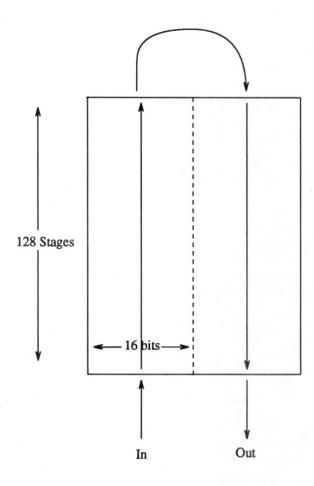

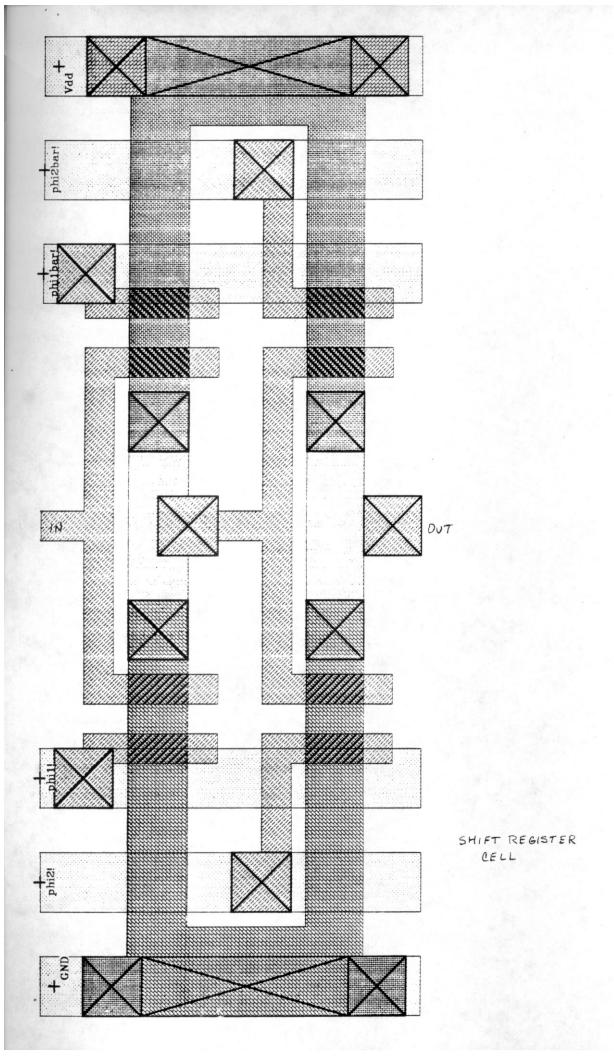

| Figure 4-8  | Shift Register Data Flow                     | 45 |

| Figure 4-9  | Neighborhood Generator Data Dependencies     | 46 |

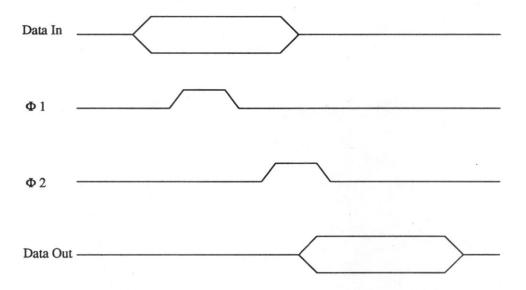

| Figure 4-10 | Chip Timing Diagram                          | 48 |

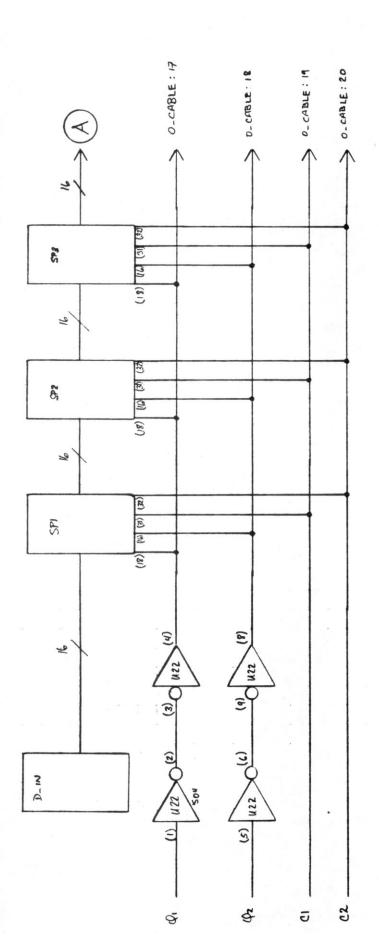

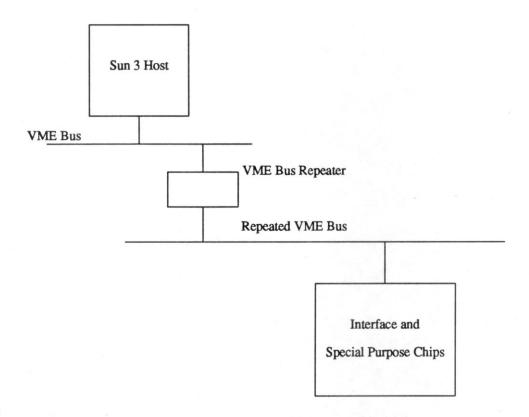

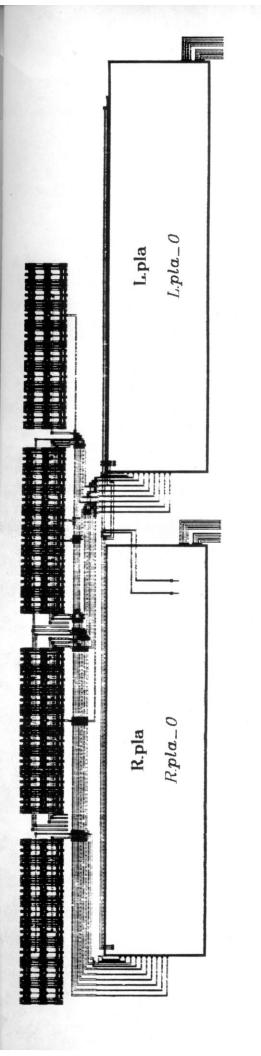

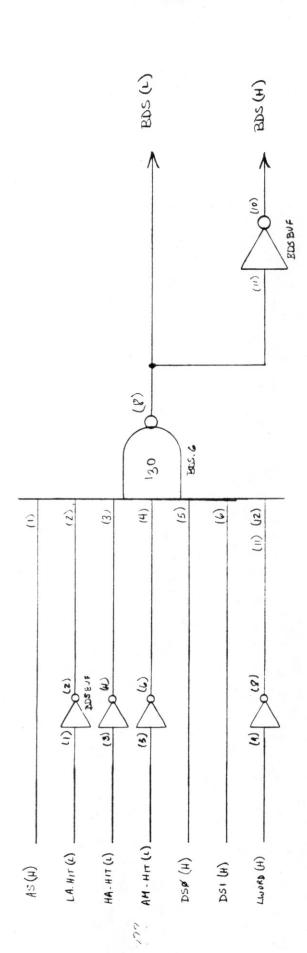

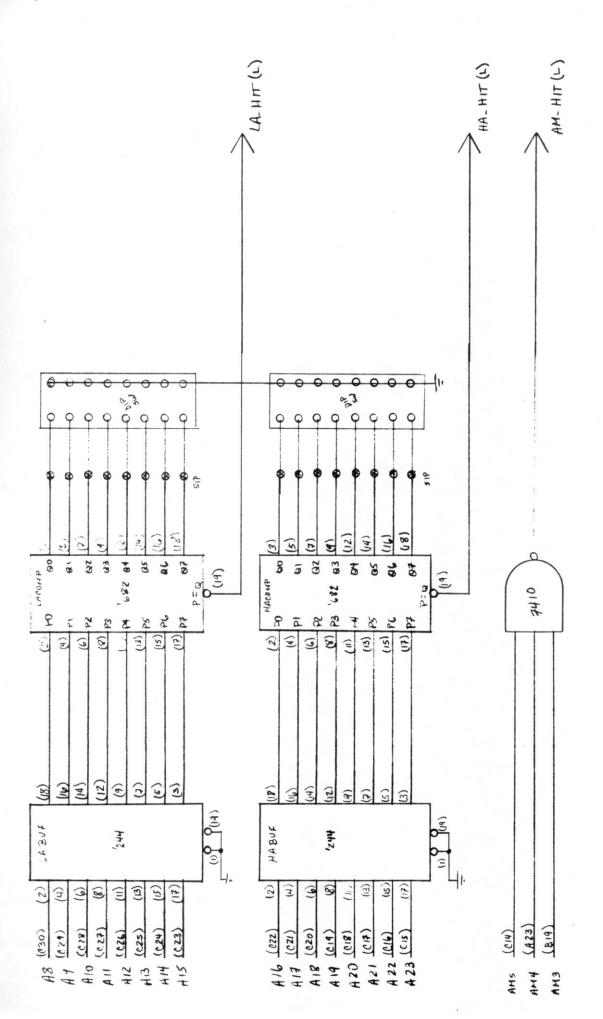

| Figure 5-1  | Basic Prototype Architectural Plan           | 51 |

| Table 5-1   | Reported Actual FHP Performance              | 65 |

| Table 6-1   | Software Entry Points                        | 71 |

## Chapter 1

## Introduction and Background

#### 1.1. History

Many problems are characterized by the fact that they deal with data values distributed on a regular mesh or *lattice*. They arise in a wide variety of applications such as image processing, computer vision, physical modeling, and the solution of partial differential equations. These problems often require tremendous computational resources and they are often solved on large supercomputers, capable of high-speed floating-point performance. However, because of their distributed nature, special purpose SIMD and MIMD processor systems have been built and applied to these problems [1-4].

Another, much simpler type of lattice computation received study in the early days of computer science: cellular automata (CA) [5]. They are thought to be able to mimic the way that computations are performed in nature because they model the simultaneous interaction of simple things distributed over a large area or volume [6].

A cellular automaton is built from the following components:

- 1) Discrete state space  $\Sigma$  over  $0 \cdot \cdot \cdot k-1$ .

- 2) Set of sites called domain  $\Delta$ . This is a discrete regular lattice in n dimensions. Each site in the domain has a value from  $\Sigma$  and this is referred to as the state of the site. The state of all the sites taken collectively is called the state of the CA.

- 3) An update rule  $\Phi$  gives the state at time t+1 from the state at time t using the state of sites from a fixed neighborhood over the n-dimensional lattice.  $\Phi$  can therefore be thought of as a local re-writing rule.

The cellular automaton originally served as a model to study self-replication in systems, and efforts were directed toward understanding the structure of the computations it supported. After a while, the interest within the computer science community died down, partly because the cellular automaton came to be viewed in the less serious light of a mathematical game and a lay scientific recreation. Stephen Wolfram, in 1984 [7], reopened this field of research with a series of papers in which he undertook a study of some properties of a class of one-dimensional cellular automata. Vastly

increased computational power made this possible. The scientific community responded with a flurry of papers on the applications of CA to real problems and the beginning of a mathematical treatment of their important properties. Today, there are conferences dedicated to the subject of cellular automata and their applications [8-15].

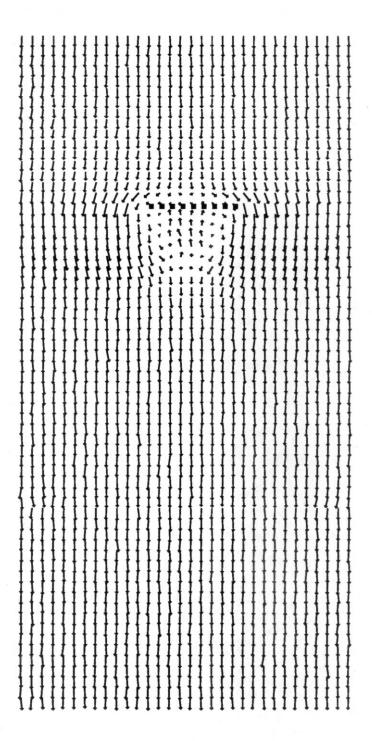

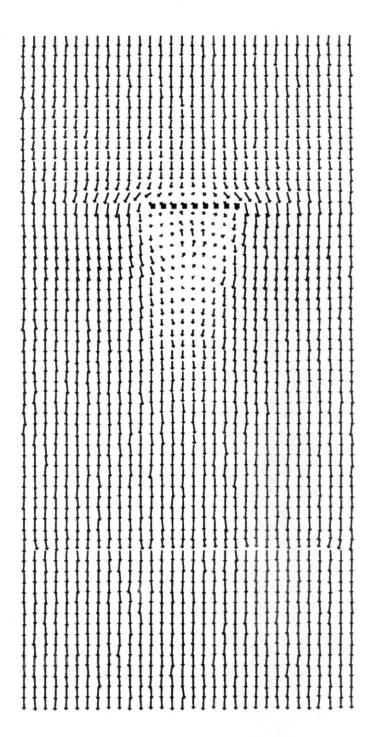

Within two years following Wolfram's 1984 papers, an idea from the mid 1960s [16] was revived by a group of researchers (Frisch, Hasslacher, and Pomeau) at Los Alamos National Laboratories [17]. In their paper they showed that in the limit of large lattice size, their automaton converges to the two-dimensional Navier-Stokes equations. They simulated their discrete particle model of a fluid by computer program and the results of the simulation bore a striking similarity to photographs of actual flow visualization studies [18]. This was perhaps the earliest concrete example of where a cellular automaton might offer a competitive alternative method of solving a hard problem in high demand: fluid dynamics. This problem had traditionally been attacked by various grid and finite element techniques in the solution of the Navier-Stokes partial differential equations [19-21].

Frisch, Hasslacher and Pomeau's demonstration sparked our interest in lattice processing architectures because it was generally held at the time that only supercomputers would offer enough computational power in the simulations of CAs to allow anything but trivial examples. We sought, as a continuation of an informal discussion group on cellular automata and an ongoing VLSI project, an architecture for high performance lattice computations that exploited custom VLSI.

This dissertation addresses the general problem of designing a high-performance VLSI-based architecture for lattice computations. We use the Frisch, Hasslacher and Pomeau (FHP) lattice gas cellular automaton, briefly described in the next section, and originally presented in [17] as the touchstone for our work because it comprises many of the properties that are characteristic of lattice computations: small storage per site, large number of sites, small neighborhood per site, and complete uniformity of the algorithm. However, unlike other special purpose architectures dedicated to problems of this genre [22-25], our architecture can, in principle, be indefinitely pipelined and extended to provide arbitrary performance on a given problem: it has the property we call *linear speedup*.

#### 1.2. The FHP Lattice Gas Model

The FHP lattice gas model is a discrete particle model for fluid dynamics [17]. It is based on a regular hexagonal lattice, giving each site six nearest neighbors. Particles move around the lattice, colliding only at lattice sites, and possibly scattering as a result. The links along which they move are bidirectional, and particles can interact only at lattice sites. Two particles traveling in opposite directions on the same link are not considered to be colliding.

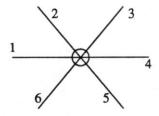

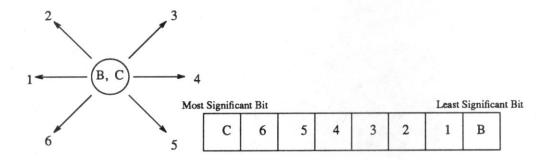

Each site has six neighbors, and outgoing particles may be present on any of these links. See Figure 1-1. Therefore each site in the lattice has 64 states. However, some models must also provide for the possibility that there is a particle at rest at the site (a "center") and, additionally, that the site

may not be part of free space, but rather may be solid. The "solid" sites are used to compose boundaries and obstacles for the simulation. This raises the minimum number of bits required to describe the state of a site from six to eight.

The links of a site are numbered:

Figure 1-1: A single site with the links numbered.

The "B" bit denotes that the site is solid and the "C" bit denotes that the site contains a particle at rest, a "center."

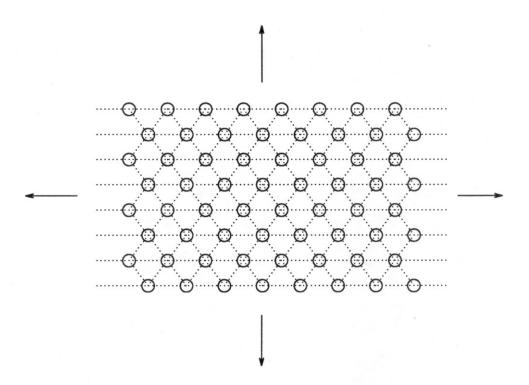

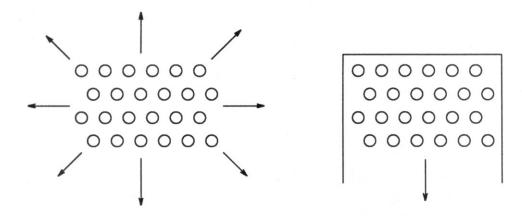

The sites in the lattice are arranged in a hexagonal lattice, as illustrated in the following diagram.

Figure 1-2: The hexagonal lattice.

#### 1.3. Scattering Rules

The particles moving in the lattice scatter at the sites according to rules that are designed to make the simulation converge to solutions of the Navier-Stokes equations. The rules have two fundamental properties: conservation of mass (particle number), and conservation of momentum. Energy need not be conserved, and in fact, this extra conservation law is not desirable because it would inhibit the damping of oscillations and instabilities by the viscosity of the fluid.

Further, the collision rules are designed to minimize a particle's mean-free-path: the number of lattice edges it traverses without colliding and scattering with another particle. The smaller the mean-free-path, the lower the viscosity of the lattice gas, and the larger the Reynolds number of the simulation. This fact lends impetus to having as many particle interactions (scattering rules) as possible. In the event that a particle cannot scatter with another when they reach a lattice site, it continues its trajectory with its previous velocity undisturbed.

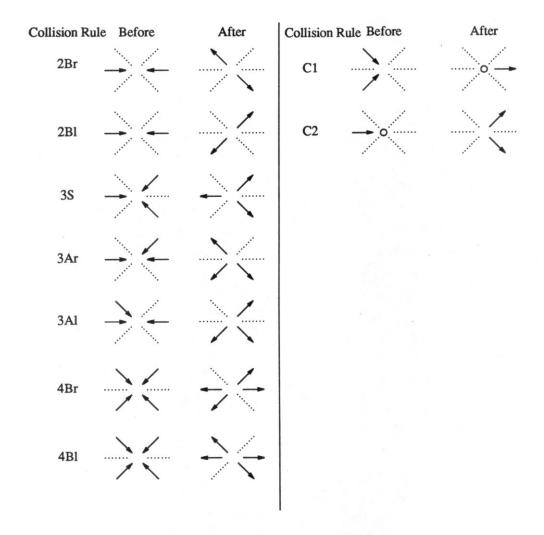

The following diagram (Figure 1-3) illustrates the particle collision rules. The configuration before the collision is shown on the left, with the configuration after the collision on the right. In the case where symmetry implies the existence of more than one member of a rule family, only one

member is shown. The complete set of rules can be derived by rotation of the before and after configurations by any multiple of 60 degrees. The small circle at the site means that a particle is present there at rest.

Figure 1-3: Particle collision rule classes

Obstacles, such as cylinders, plates, or wings, are placed in the lattice by changing a site from "free-space" to "solid." While a "free-space" site scatters particles according to the rules outlined above, a "solid" site behaves differently and there are several permissible choices. The simplest possibility is to have each particle reflect back along its incoming path. Another possibility is to have each particle reflect in such a way that its incident angle equals its reflected angle. Unfortunately, the latter entails having different kinds of solid sites, depending on position in an object.

These two choices also correspond to different kinds of boundary layer effects [17]. In the first case, the rule leads to a "no-slip" boundary, where the velocity of the fluid near a surface is zero. The

second case corresponds to a "slip" condition; the fluid next to a boundary can move. We adopt the "no-slip" boundary because it is simpler, and more realistic for the kinds of fluid dynamic phenomena that we expect to simulate.

Three of the rule classes, 2B, 3A, and 4B have L and R variants, so called because they scatter left-ward and right-ward respectively. It is critical that both of these scatterings take place with equal probability or a systematic bias will be introduced that will destroy the convergence properties of the simulation. When the simulation is performed in software, it is a simple matter to "flip a coin" and choose either an L or an R rule when appropriate. Alternatively, the software simulation can use the R rule during even-numbered generations and the L rule during the odd-numbered ones (or vice-versa). In hardware, however, it is undesirable to "flip a coin" or to change rules on every generation. Instead, one of the chip's two processors performs the R rules all the time, and the other performs the L rules. This has the effect of placing the L and R rules throughout the lattice in a manner similar to the squares of a checkerboard. The unbiased spatial distribution is equivalent (informally) to an unbiased temporal distribution (coin flipping) because the events of interest occur randomly throughout the lattice and the simulation.

The sequence in which particle collisions are computed at lattice sites is also critical to the success of the simulation. In concept, the entire lattice is updated simultaneously, with each update called a *generation*. In practice, the new site values can be computed in any sequence provided that particles from generation i are the only ones used to compute particle velocities for generation i+1. If this rule is violated, it is easy to give a configuration and a site update sequence that violates the mass (and therefore the momentum) conservation law [17].

The behavior of a single particle in the lattice is effectively random, but it is correlated with the behavior of other nearby particles. The speed of any particle in the lattice is unity, but the simulation is intended to model a continuous process. The net velocity of an ensemble of particles over a small region of the lattice (spatial averages) yields the hydrodynamic behavior that is sought. This function is not computed by the Lattice Gas Cellular Automaton (LGCA) chip; it is done as part of a post-processing phase after computation has taken place.

One question that remains before processing can be fully understood is: What is done with the edges of the lattice? Again, there are several possibilities. The edges can be pair-wise attached so that the lattice has the structure of a torus (Figure 1-4). This has the effect of replicating the simulation an infinite number of times in all directions.

Figure 1-4: Toroidal Lattice

In some cases this mirroring could be considered undesirable. It might be preferable to make the finite lattice appear as if it were part of an infinite plane of fluid. Under certain conditions, this is possible. The key idea is that the links on the edges of the lattice should "see" incoming particles distributed as though the fluid extended infinitely in all directions, with a uniform velocity field. Let the average density of particles in the lattice be d. Put another way, d is the probability that a particle is found on a given link at any site in the lattice. Assume that there is a uniform velocity field  $\vec{\nabla}$ , and that the links point in directions  $\vec{a}_1, \ldots, \vec{a}_6$ . It can be shown that the probability of finding a particle on link i is approximately [26]

$$P_{i} = d \left[ 1 + \frac{7}{3} \overrightarrow{v} \cdot \overrightarrow{a}_{i} - \left[ \frac{7}{6} \frac{1 - 2d}{1 - d} \left[ \overrightarrow{v}^{2} - \frac{7}{3} (\overrightarrow{a}_{i} \cdot \overrightarrow{v})^{2} \right] \right] \right]$$

(1-1)

The probability of finding a particle at rest at a site is given by Equation (1-1) with  $\vec{a}_i \cdot \vec{v} = 0$ .

If particles are introduced at the edges of the lattice with probabilities given by Equation (1-1), then the lattice appears to be embedded in an infinite plane of fluid which is moving at velocity  $\vec{v}$ .

#### 1.4. Summary of Results

This dissertation is divided into two parts. Part I (Chapters 2 and 3) discusses the theoretical and analytical underpinnings of this work. Chapter 2 presents an analysis technique for determining the design space of architectures geared for lattice computations and based in VLSI. We derive the allowable design space based on the input/output limitation of the VLSI technology.

The architecture that we implemented can theoretically provide an arbitrarily high site update rate by concatenating any number of chips into a single pipeline. However, there is the question of whether or not this can actually be done in practice. In the course of developing the custom chips and the rest of the lattice gas system, we posed the following question: Can a linear pipeline be made arbitrarily deep or is there some point at which linear speedup breaks down and becomes sub-linear? Two factors that seemed reasonable candidates for causes of failure are timing and reliability.

The first, timing, has been studied extensively. Numerous clocking schemes are known and questions of synchronization and synchronization failure have been examined. However, there was little information available on a model that describes how problems might accumulate as systems increase in size. In fact, the only paper which we found that began to address such questions was [27].

Chapter 3 proposes and analyzes a probabilistic model for the accumulation of clock skew in large, synchronous, multiple processing element systems. Using this model, we derive upper bounds for expected skew, and its variance, in tree distribution systems with N synchronously clocked processing elements.

We apply these results to two specific models for clock distribution. In the first, which we call *metric-free*, the skew in a buffer stage is Gaussian with a variance independent of wire length. In this case the upper bound on skew grows as  $\Theta(\log N)$  for a system with N processing elements.

The second, *metric*, model, is intended to reflect VLSI constraints: the clock skew in a stage is Gaussian with a variance proportional to wire length, and the distribution tree is an H-tree embedded in the plane. In this case the upper bound on expected skew is  $\Theta(\sqrt{N\log N})$  for a system with N processors. Thus the probabilistic model is more optimistic than the deterministic summation model of Fisher and Kung [27], which predicts a clock skew  $\Theta(N)$  in this case, and is also consistent with their lower bound of  $\Omega(\sqrt{N})$  for planar embeddings.

We have estimates of the constants of proportionality, as well as the asymptotic behavior, and we have verified the accuracy of our estimates by simulation. This shows that clock skew grows as a function of system size, and system timing can limit the ultimate size of synchronous, two dimensionally organized processor systems.

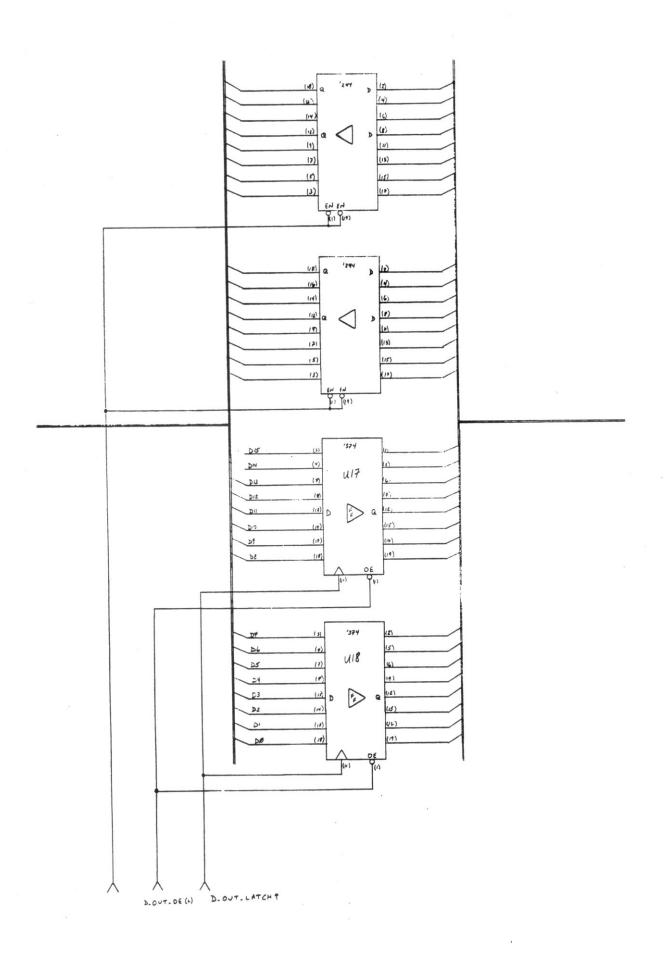

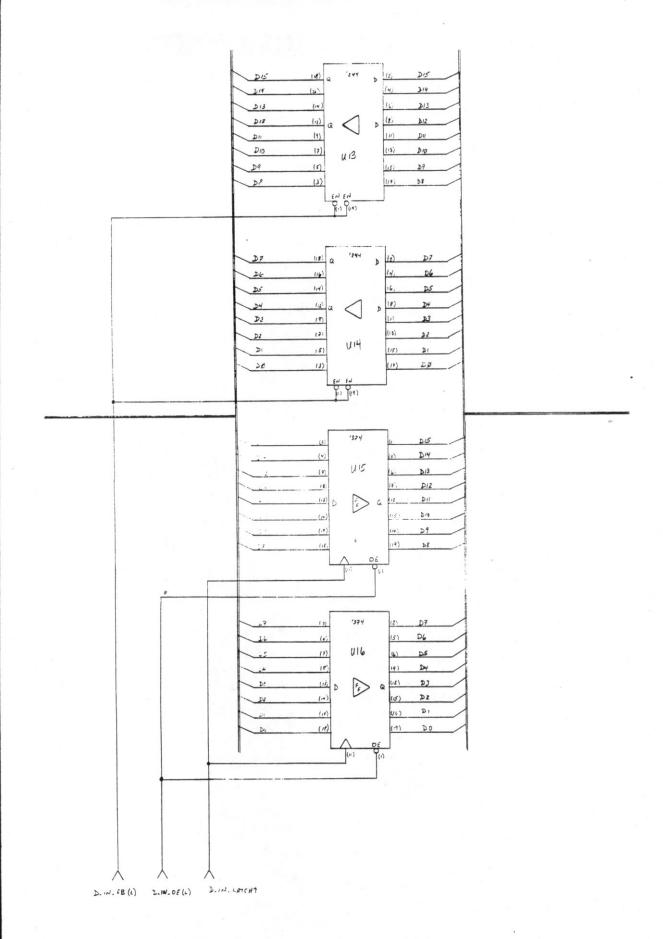

Part II (Chapters 4 through 6) discusses the practical experience of implementing a system based on a custom CMOS chip that simulates the FHP lattice gas. Chapter 4 describes the architecture and implementation of the Lattice Gas Cellular Automaton (LGCA) chip which is a CMOS VLSI

processor that provides 14 million site updates per second. The chips can be pipelined for even higher performance, and it is theoretically possible to build a special purpose device that can provide the computational equivalent of a CRAY XMP-48 supercomputer or a Thinking Machines, Inc. Connection Machine for this problem.

To demonstrate the feasibility of such an undertaking, we have constructed a prototype, called LGM-1, which uses ten of these chips arranged in a pipeline. The LGM-1 computes approximately 7 million site updates per second, which is only 5% of the maximum throughput of the 10 VLSI chips. The discrepancy in performance levels is caused by the simple, low-bandwidth system interface and the relatively small power of the Sun 3 workstation host.

Chapter 5 describes the hardware that we built to allow a Sun 3 workstation to act as a host for our special purpose processor pipeline. Having had this experience, we gave some thought to the prototyping process as a whole. This leads us to Chapter 6, which describes a proposed prototyping environment which is sufficiently general to support chips fabricated by other designers. Its basic philosophy is that it is more profitable to be able to add hardware easily than it is to make the underlying system as fast as possible.

We conclude with Chapter 7, which summarizes and reviews the important results of this work. It also outlines future tasks for the continuation of the work begun with this thesis.

#### 1.5. Previously Published Material

Chapter 2 is taken from the first half of a paper that was co-authored with Richard Squier and Kenneth Steiglitz and appears in its entirety in [28]. This work was supported in part by NSF Grant ECS-8414674, U. S. Army Research Office-Durham Contract DAAG29-85-K-0191, and DARPA Contract N00014-82-K-0549.

The results in Chapter 3 have been accepted for presentation at the International Conference on Systolic Arrays to be held in San Diego, California on May 25-27, 1988 and have been submitted for publication in the *IEEE Transactions on Computers*. This work was supported by NSF Grant MIP-8705454, U. S. Army Research Office-Durham Contract DAAG29-85-K-0191.

The material in Chapters 4 and 5 has been presented at the 22nd Conference on Information Sciences and Systems held in Princeton, NJ on March 16-18, 1988.

## Chapter 2

## Analysis of Lattice Architectures

#### 2.1. Introduction

This chapter deals with the problems of designing and building practical, custom VLSI-based computers for lattice calculations. These computational problems are characterized by being iterative, defined on a regular lattice of points, uniform in space and time, local, and relatively simple at each lattice point. Examples include numerical solution of differential equations, iterative image processing, and cellular automata. The recently studied lattice gas automata, which are microscopic models for fluid dynamics, are proposed as a testbed for the work.

The machines envisaged — lattice engines — would typically consist of many instances of a custom chip and a general-purpose host machine for support. In many practical situations, the performance of such machines is limited, not by the speed and size of the actual processing elements, but by the communication bandwidth on- and off-chip, and by the memory capacity of the chip.

A familiar example of lattice-based computational tasks is two-dimensional image processing. Many useful algorithms, such as linear filtering and median filtering, recompute values the same way everywhere on the image, and so are perfectly uniform; they are local in that the computation at a given point depends only on the immediate neighbors of the point in the two-dimensional image.

Another class of calculations, besides being uniform and local, have the additional important characteristic of using only a few bits to store the values at lattice points, and so are extremely simple. Further, they operate on local data iteratively, which means that they are not as demanding of external data as many signal processing problems. These computational models — uniform, local, simple, and iterative — are called *cellular automata*. We will next describe a particular class of cellular automata, one that provides a good testbed for the general problems arising in the design of dedicated hardware for lattice-based computations.

#### 2.2. A paradigm for lattice computations: the lattice gas model

Quite recently, there has been much attention given to a particularly promising kind of cellular automaton, the so-called *lattice gases*, because they can model fluid dynamics [29]. These are lattices governed by the following rules:

- At each lattice site, each edge of the lattice incident to that site may have exactly zero or

one particle traveling at unit speed away from that site, and, in some models, possibly a

particle at rest at the lattice site.

- There is a set of collision rules which determines, at each lattice site and at each time step, what the next particle configuration will be on its incident edges.

- The collision rules satisfy certain physically plausible laws, especially particle-number (mass) conservation, and momentum conservation.

These lattice gas models have an intrinsic exclusion principle, because no more than one particle can occupy a given directed lattice edge at any given time. It is therefore surprising that they can model fluid mechanics. In fact, in a two-dimensional hexagonally connected lattice, it has been shown that the Navier-Stokes equation is satisfied in the limit of large lattice size. This model is called the FHP model, after Frisch, Hasslacher, and Pomeau [17]. The older HPP [30] model, which uses an orthogonal lattice, does not lead to isotropic solutions [17].

The idea of using hexagonal lattice gas models to predict features of fluid flow seems to be about two years old, and whether the general approach of simulating a lattice gas can ever be competitive with more familiar numerical solution of the Navier-Stokes equation is certainly a premature question. Extensions to three dimensional gases are just now being formulated [31], and quantitative experimental verification of the two-dimensional results is fragmentary. The Reynolds numbers achievable depend on the size of the lattices used, and very large Reynolds numbers will require huge lattices, and correspondingly huge computation rates. For a discussion of the scaling of the lattice computations with Reynolds number, see [32].

What is clear is that the ultimate practicality of the approach will depend on the technology of special-purpose hardware implementations for the models involved. Furthermore, the uniformity, locality and simplicity of the model mean that this is an ideal testbed for dedicated hardware that is based on custom chips. We will therefore use the lattice gas problem as a running example in what follows. We especially want to study the interaction between the design of custom VLSI chips and the design of the overall system architecture for this class of problems.

We will present and compare two competing architectures for lattice gas cellular automata (LGCA) computations that are each based on VLSI custom processors. The analysis will focus on the permissible design space given the usual chip constraints of area and pin-out and on the achievable performance within the design space.

#### 2.3. Serial Pipelined Architectures for Lattice Processing

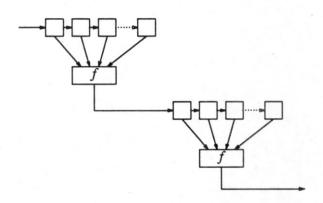

We are primarily interested in special-purpose, VLSI-based processor architectures that have more than one PE ( $processing\ element$ ) per custom chip. It is important to recognize that if the PE's are not kept busy, then it might be more effective (in terms of overall throughput) to have fewer PE's per chip but to use them more efficiently. Although there are many architectures that have the property of using PE's efficiently, we will describe only two, both based on the idea of serial pipelining (see Figure 2-1). The boxes containing the letter f are processing elements that compute the function f. The other boxes represent memory that is local to the processor.

This approach has the benefit that the bandwidth to the processor system is small even though the number of active PE's is large. The serial technique has been used for image processing where the size of the two-dimensional grid is small and fixed [11, 33, 34], and has also been used to design a high performance custom processor for a one-dimensional cellular automaton [35].

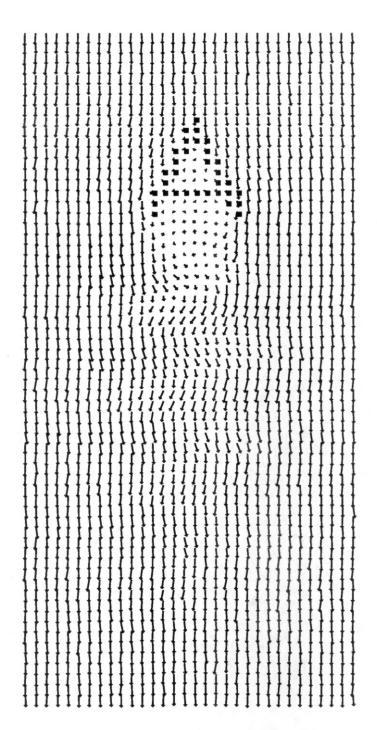

Figure 2-1: One-Dimensional Pipeline

Consider what is required to pipeline a computation. We must guarantee that the appropriate site values of the correct ages are presented to the computing elements. In the case of the LGCA, we can express this data dependency as:

$$a_i^{t+1} = f(N(a_i^t))$$

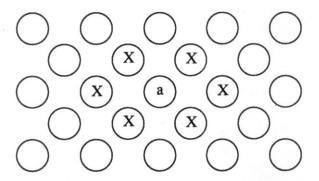

where  $a_i^t$  is the value at lattice site  $a_i$  at time t,  $N(a_i^t)$  is the neighborhood of the lattice site  $a_i$  at time t, and f is the function that determines the new value of  $a_i$  based on its neighborhood. The LGCA requires all the points in the neighborhood of a to be the same age in order to compute the new value,  $a_i^{t+1}$ . The LGCA has a neighborhood that looks like:

Figure 2-2: Hexagonal Neighborhood

The sites marked with X constitute the neighborhood of site a.

One-dimensional pipelining also requires a linear ordering of the sites in the array. That is, we wish to send the values associated with the sites one at a time into the one dimensional pipeline and receive the sequence of sites in the same order possibly some generations later. Therefore, we would like sites that are close together in the lattice to be close together in the stream. In this way, the serial PE requires a small local memory because neighborhoods (sites that are close together in the array) will also be close together in the stream. Unfortunately, the Lattice Gas Automaton can require a large amount of local memory per PE because there is no sub-linear embedding of an array into a list [36].

The natural row-major (raster scan) embedding of the array into a list preserves 2-neighborhoods\* with diameter 2n-2. This means that a full neighborhood of a site from an  $n \times n$  lattice is distributed in the list so that some elements of the neighborhood are at least 2n-2 positions apart. This embedding is undesirable for two reasons. The amount of local memory required by a PE is a function of the problem instance, forcing us to decide in advance the size of one dimension of the lattice (one can actually process a prism array, finite in all but one dimension) because the chip will only work for a single problem size due to its fixed span. The second deficiency is due to the size of the span. If n=1000, then each PE would require about 2000 sites worth of memory. This puts a severe restriction on the number of PE's that can be placed on a chip.

Unfortunately, the 2n-2 embedding is optimal. Rosenberg showed this bound holds for prism array realizations but it has been unknown whether it is possible do better for finite array realizations. Rosenberg's best lower bound for the finite array case has never been achieved and he suspected that the row-major scheme was optimal. Sternberg [37] also questioned whether or not the storage requirement for a serial pipelined machine could be reduced. Supowit and Young [38] showed that the row-major embedding is optimal and therefore a serial pipeline must use at least 2n-2 storage.

<sup>\*</sup>Sites that are two edge traversals apart in the lattice

**Theorem 2-1:** Place the numbers  $1, \ldots, n^2$  in a square array a(i, j), and define the *span* of the array to be

$$\max \left\{ ||a(i+1,j)-a(i,j)||, ||a(i,j+1)-a(i,j)|| \right\}$$

Then span  $\geq n$ .

**Proof:** Put the numbers in the array one at a time in order, starting with 1. When, for the first time, there is either a number in every row or a number in every column, stop. Without loss of generality, assume this happens with a number in every row.

We claim that there cannot be a full row. Suppose the contrary. The last number entered was placed in an empty row, so there must have been a full row before we stopped. This would mean there was a number in every column before there was a number in every row.

Since there is no full row, but a number in every row, there is at least one vacant place in every row that is adjacent to an occupied spot. Choose one such vacant place in each row, and call them set F (with |F| = n). Now if we stopped after placing the number t, the places in F will get filled with numbers greater than t. The largest number that will be put in a location in F is  $\geq t+n$ , and will be adjacent to a number  $\leq t$ .  $\square$

The appealing aspects of the serial architecture are the simplicity of its design, its small area in comparison to other architectures, and the small input/output bandwidth requirement. The computation proceeds on a wavefront [39] through time and space, each succeeding PE using the data from the previous PE without the need for further external data.

#### 2.4. Wide Serial Architecture (WSA)

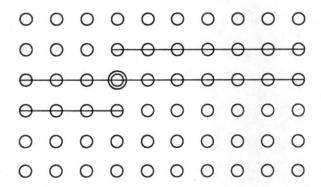

Assume that data from the two dimensional array is serialized by a row major raster scan. Throughput in a serial architecture can be improved by adding concurrency at each level of the pipeline. One way to accomplish this is to have each pipeline stage compute the new value of more than one site each clock period. For example, if the computation at PE j is at the point where site a, circled, is to be updated, then PE j contains the data indicated by strike-out in the following:

We could allow a second PE j' to compute site a+1 at the same time if we store just one more data point.

The most attractive feature of this scheme is that performance is increased, but at a cost of only the incremental amount of memory needed to store the extra sites. The on-chip memory per PE is also reduced dramatically, decreasing linearly with the number of PE's per chip. However, there is a price to pay: two new site values are required every clock period so that two site updates can be performed. The extra PE's require added bandwidth to and from the chip and this implies that the main memory system must provide that bandwidth as pins or wires.

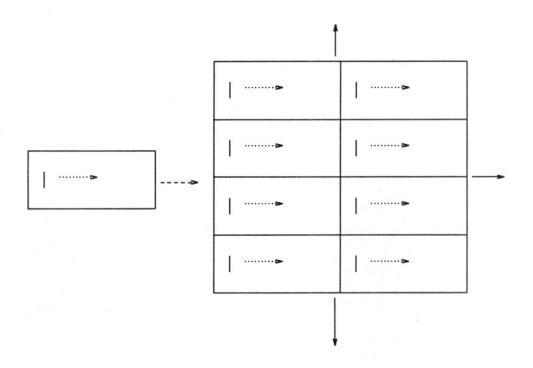

As an example, the following figure shows how two PE's on the same chip can cooperate on a computation. Each square of the shift register memory holds the value of one site in the lattice. Every clock period, two new site values are input to the chip, two sites updated and their values output to the next chip in the pipeline.

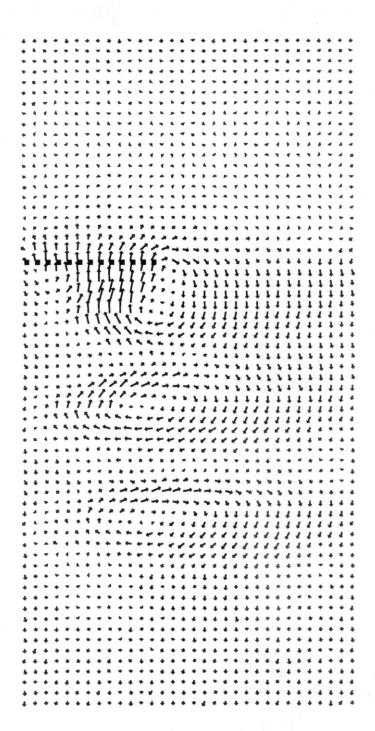

Figure 2-3: Wide Serial Architecture

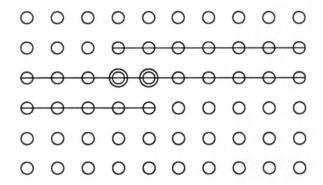

#### 2.5. Sternberg Partitioned Architecture (SPA)

In [37] Sternberg proposes that a large array computation can be divided among several serial processors, each of which operates as described earlier. The array is divided into adjacent, non-overlapping columnar slices and a fully serial processor is assigned to each slice (see Figure 2-4).

The processors are not exactly the same as those described above; they are augmented to provide a bidirectional synchronous communication channel between adjacent partitions so that sites

Figure 2-4: Sternberg Partitioned Architecture

whose neighborhoods do not lie entirely in the storage of a single PE can be computed correctly and in step with other site updates. See [37] for details.

Dividing the work in this way accomplishes three things. First, it decreases the amount of storage that each PE needs in order to delay site values for correct operation of the pipeline. This comes about because each PE needs to delay only two lines of its slice, not of the whole line width. Second, it increases the ratio of processing elements to the total number of sites, permitting an increase in the maximum throughput by a multiplicative constant equal to the number of slices. Third, it provides a degree of modularity and extensibility. It is possible to join two smaller machines along an edge to form a machine that handles a larger problem.

In the case of a VLSI implementation, decreasing the size of the local storage is extremely important because most of the silicon area in the implementation of a serial processor is shift register. Since each PE in the SPA architecture requires fewer shift register storage cells, it is possible to place several PE's on a chip, whereas if each serial PE were required to store two lines of the whole lattice, then only one or two PE's could be placed on a VLSI chip with current technology. The only way around this limitation is to use another technology to implement the required storage, such as off-chip commercial memories, in which case we quickly encounter pin limitations.

It is important to recognize that the *total* amount of storage required under this organization is two lines of the whole lattice per pipeline stage. Thus the total storage requirement under this implementation is not reduced below that of the fully serial approach presented earlier. In addition, each column of serial processors requires its own data path to and from main memory, and this data path is a relatively expensive commodity.

#### 2.6. Analysis and Comparison of WSA and SPA

In this section we analyze and compare the Sternberg partitioned architecture (SPA) with the wide-serial architecture (WSA) that we proposed in Section 4. The analysis derives the optimum throughput and area of processing systems composed of VLSI chips for the two-dimensional FHP lattice gas problem. We define the design parameters for each system and derive the design curves and optimum values of those parameters. For the analysis, we assume that a memory system capable of providing full bandwidth to the processor system is available. Finally, we compare the systems on the basis of maximum throughput, total system area, and throughput-to-area ratio. We also discuss the relative advantages and disadvantages of both architectures with an emphasis on system complexity and ease of implementation.

#### 2.7. Wide-Serial Architecture (WSA)

The wide-serial architecture (WSA) has system parameters: (assumes 1 pipeline stage per chip, *P* processing elements wide)

$$N = k$$

chips (System Area) (2-1)

$$R = F \cdot P \cdot k \frac{sites}{second}$$

(System Throughput) (2-2)

and chip constraints

$$2D \cdot P \le \Pi$$

(Chip Pins) (2-3)

$$\beta(2L+7P+3) + \gamma P \le \alpha$$

(Chip Area) (2-4)

where

This is a very important assumption.

N is the total number of chips constituting the processor,

P is the number of PE's per VLSI chip,

k is the total depth in PE's of the processor pipeline (path length),

F is the major cycle time of the chip,

D is the number of bits required to represent the state of a lattice site,

L is the number of sites along an edge of the square lattice,

$\Pi$  is the total number of pins usable for input/output,

$\beta$  is the area of a shift register that holds a site value, in  $\lambda^2$ ,

$\gamma$  is the area of a PE, in  $\lambda^2$ ,

$\alpha$  is the total usable chip area, in  $\lambda^2$ .

For convenience, we also define:

$$B = \frac{\beta}{\alpha}$$

= normalized site storage area

$$\Gamma = \frac{\gamma}{\alpha}$$

= normalized processor area

Less formally, this says that the number of chips that we need for the processor equals the total pipeline depth required, k. The processing rate that this system achieves is equal to the depth of the pipeline, multiplied by the number of processors at each depth, multiplied by the rate at which a processor computes new sites. We are assuming that each VLSI chip will contain only a single wide parallel pipeline stage. That is, the chip is not internally pipelined with wide-serial processors.

We wish to maximize R subject to having a fixed number of chips,  $N = N_0$ , and subject to constraints on the pin count and area of the VLSI custom chip. Notice that the problem is equivalent to maximizing P subject to the chip constraints because  $R = F \cdot P \cdot k = F \cdot P \cdot N$ , where F and N are fixed (N is fixed at  $N_0$ ).

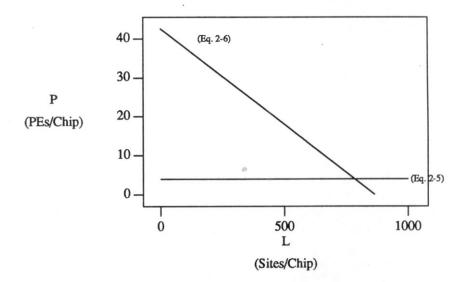

The constraints are described in the *L-P* plane by the following two inequalities:

$$P \le \frac{\Pi}{2D} \tag{2-5}$$

$$P \le \frac{1 - 3B - 2BL}{7B + \Gamma} \tag{2-6}$$

If we consider an example where D = 8,  $\Pi = 72$ ,  $B = 576 \times 10^{-6}$ , and  $\Gamma = 19.4 \times 10^{-3}$  (figures derived from our actual layouts) we get the following graph:

The chip constraints require that the operating point determined by P and L lie below both curves. The intersection of the two curves is  $P \approx 4$  and  $L \approx 785$ . Beyond that point, we need to decrease the number of processors on a chip to make room for more memory — an undesirable situation because throughput then drops off linearly. Furthermore, we want L to be as big as possible, so the corner is the logical choice of operating point.

We are also interested in the ultimate maximum performance that the architecture can deliver using any number of chips. It is easy to see that the maximum throughput for a fixed clock frequency, F, comes when the pipeline depth, k, is at a maximum. A maximum value,  $k_{\max} = L$ , arises because at that point the pipeline contains all the values of the sites in the lattice and there is no new data to introduce into the processor pipeline. The maximum values for processor system area and processor system throughput are therefore:

$$N_{\text{max}} = L \quad chips$$

(2-7)

$$R_{\text{max}} = \frac{\Pi}{2D} \cdot F \cdot L \quad \frac{\text{sites}}{\text{sec}}$$

(2-8)

It is also interesting to note that there is an upper bound on L even if we were to accept arbitrarily slow computation. At a certain point all the chip area would be used for memory, leaving no room for PE's.

The major limitation of this architecture is that the largest problem instance is fixed by the chip technology, but it has the redeeming features of simplicity, ease of implementation, and small main memory bandwidth.

#### 2.8. Sternberg Partitioned Architecture (SPA)

This processor computes updates for a lattice L sites on a side by partitioning the lattice into non-overlapping slices that are each W sites wide (there are  $\frac{L}{W}$  such slices). Each of the VLSI chips that compose the processor computes  $P_w$  slices and the computation of each slice is pipelined on the chip to a depth  $P_k$  (see Figure 2-4). It is then easy to see that the system has area and throughput:

$$N = \frac{L}{P_w} \cdot \frac{k}{P_k} \quad chips$$

(System Area) (2-9)

$$R = F \cdot k \cdot \frac{L}{W} \quad \frac{\text{sites}}{\text{sec}}$$

(System Throughput) (2-10)

To derive the constraints on the VLSI chip, notice that the communication path between chips in the direction of the data pipeline requires  $2DP_w$  pins, and that the "slice to slice" path requires  $2EP_k$ , where E is the number of bits required to complete the information contained in a single site's neighborhood, when that neighborhood is split across a slice boundary. However, the chip must use no more than  $\alpha$  area, of which processors each require  $\gamma$ , and memory to hold a site value requires  $\beta$ . Thus the whole chip is governed by the constraints

$$2DP_w + 2EP_k \le \Pi$$

(Chip Pins) (2-11)

$$((2W+9)\beta + \gamma)P_wP_k \le \alpha \qquad (Chip Area) (2-12)$$

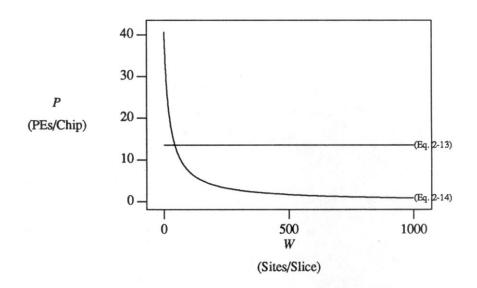

We again wish to maximize throughput with respect to a fixed number of chips,  $N = N_0$ , while at the same time satisfying the VLSI chip constraints of area and bandwidth. This again turns out to be equivalent to maximizing the total number of processors on the chip because we can easily verify by direct substitution that  $R = F \cdot k \cdot \frac{L}{W} = P_w P_k \cdot F \cdot N_0$ . Since F and  $N_0$  are fixed, it suffices to maximize the product  $P_w P_k = P$  subject to the constraints above.

To evaluate the design space of SPA, it is helpful to view it in the W-P plane. We do this via a change of variables:

$$P = P_{w}P_{k}$$

.

Rewriting the chip inequalities yields:

$$2DP_{w} + 2E\frac{P}{P_{w}} \le \Pi \tag{2-13}$$

$$((2W+9)B + \Gamma)P \le 1$$

(2-14)

where  $P_w$ , P, and W are variables. This is the logical choice of variables for this architecture because they are the ones that are constrained by the chip technology and govern the optimal design of the chip. Once we know good values for them, a machine which can compute for an arbitrary lattice

width L can be built by increasing the number of slices of width W.

When these curves are projected onto the W-P plane using the values for D,  $\Pi$ , B from the previous example; and setting E to 3 (three bits must be passed to complete an LGCA neighborhood) we have:

The constant curve is a projection of the first constraint where  $P_w$  is given the value which permits P to achieve its maximum value. For this example, this occurs at  $P_w = \frac{9}{4}$ . As before, we need to operate below both curves, and the corner at  $P \approx 13.5$  and  $W \approx 43$  yields the best choice. Beyond this point, throughput drops off quite rapidly as the silicon real estate is used by memory.

#### 2.9. Discussion

The above analysis gives us two different viewpoints from which to make a comparison between these two architectures. Ignoring extensibility, we can make a comparison between the two designs when they are optimized for throughput, as they were in the preceding analysis. To include extensibility as a criterion, we can make the comparison by using a slight variant of WSA which allows for extensibility by sacrificing processing speed.

First, let us compare the designs optimized for throughput without regard to extensibility. The optimal WSA configuration limits the lattice length to L = 785. Both systems, WSA and SPA, have throughput rates which grow linearly with the number of chips. However, SPA is three times faster than WSA (SPA has twelve processors per chip while WSA has four). On the other hand, the SPA system requires four times as much main memory bandwidth as the WSA system: 262 bits/tick versus 64 bits/tick.

The above argument contains a bias in favor of SPA. System timing is an important consideration which can make it difficult to clock SPA as fast as WSA. The WSA architecture has connectivity only in one dimension whereas the SPA system requires communication in both the pipeline direction and the synchronous side-to-side data paths. This added complexity is a more pronounced drawback for SPA when extensibility is considered, as we will mention below. The conclusion in both cases favors the WSA system when it comes to considering an implementation. There is also the matter of the data access pattern in the memory. The WSA machine accesses the data in a strict raster scan pattern which is simpler than the row-staggered pattern that the SPA scheme requires for its operation.

The SPA architecture has one considerable advantage over the WSA scheme: extensibility. Smaller instances of an SPA machine can be joined together to form a machine that computes a larger lattice. This is not true for the WSA case, where computation is limited to lattice sizes which do not exceed L as given by the chip area constraint, because all the required data must fit on the chip. This requirement is relaxed in the SPA scheme because data can be moved between adjacent chips as W is adjusted to the chip constraints and an arbitrary lattice width L can be supported by composing a suitable number of slices. In this respect the two schemes seem incomparable.

Our second point of view on the comparison of these two architectures is facilitated by considering a slight variation of WSA which allows extension of the lattice size. The extension can be accomplished by moving a portion of the shift register off chip. The pin constraints given previously, with the same constants, allow only one processor per chip in this case. A stage in the pipeline consists of a processor chip and associated shift registers sufficient to hold the remainder of the 2L + 10 node values which do not fit onto the processor chip. We will call this version of WSA WSA-E.

Both systems, SPA and WSA-E, have throughput rates that grow linearly with the number of chips in the system for a fixed lattice size L. However, the constant of proportionality between the two rates grows with increasing lattice size. The reason is that the number of processors per unit chip area is independent of lattice size for SPA, whereas it decreases with increasing lattice size for WSA-E. So, for instance, given the same number of chips and a lattice size  $L \le 785$ , the SPA system is twelve times faster than WSA-E because it has twelve processors per chip as opposed to one per chip.

A better understanding of the contrasts between the two systems can be obtained by looking at requirements for main memory bandwidth and storage area per processor. WSA-E has a constant bandwidth requirement of 16 bits per clock tick and requires (2L + 10)B storage area per processor; SPA has a main memory bandwidth requirement of  $\frac{L}{3}$  bits per tick and requires (1284)B area per processor. For a fixed processing rate the penalty for larger lattice size is either linear growth in the number of chips for the WSA-E system, or linear growth in the main memory bandwidth in the SPA case. For example, if L = 1000, then WSA-E requires about twice as much area as SPA, while requiring about one twentieth as much bandwidth.

#### 2.10. Summary

The technique described in this chapter can be used to analyze other architectures. It offers a systematic way to arrive at important system parameters. Its greatest limitation is that it depends on constants of proportionality and offers no meaningful asymptotic information. It also requires that the design has progressed at least as far as the layout of certain basic cells so that areas can be used in calculations.

Another limitation is that the technique neglects interconnection and wiring area, which we later found to have significant effect. It reduced the number of PEs from 4 to 2 and the line length, L, from 785 to 512 in our actual implementation (see Chapter 4).

The assumption that the required memory bandwidth is always available from the host is not realistic. Initially, we had included a parameter which characterized the host/PE bandwidth mismatch. However, the algebra obscured the analysis and comparison, and we therefore chose to present only the simplified presentation.

Nevertheless, this analysis provided enough information to help us choose our implementation and rule out alternate architectures. Given the simplicity and directness of WSA, and given that performance could be increased almost arbitrarily by cascading chips, we decided to implement the WSA architecture.

## Chapter 3

### A Probabilistic Model For Clock Skew

#### 3.1. Introduction

The accumulation of clock skew, the differences in arrival times of signals in a computing system with a central clock, is one of the factors that limit the speed of such systems. While some researchers have attempted to describe the underlying physical causes of skew [40,41], there is little published material describing models of skew accumulation and the asymptotic behavior of skew with increasing system size.

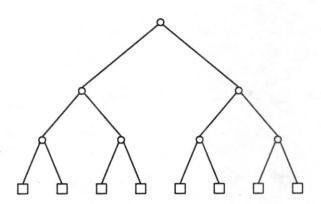

Fisher and Kung in [27] present two models and derive bounds on clock skew under each. They assume, in each case, that the global clock is distributed via a rooted binary tree of buffers and wires.

The first of their two models, the "difference model," specifies that the skew between two clocked nodes is proportional to the difference in the path lengths from each clocked node to their nearest common ancestor in the distribution tree. "Path length" means the actual geometric length, not the number of edge traversals in a representative graph. Under this model, both one and two-dimensional arrays can be clocked without skew by distributing the global signal via a topology that has equal path length to each clocked node. An H-tree is just one example of such a topology.

The second model, the "summation model," is less optimistic. It states that the skew between two clocked nodes is proportional to the sum of the path lengths from each node to their nearest common ancestor. Using this model, Fisher and Kung were able to show that one-dimensional arrays of processors can be clocked with a constant amount of skew, whereas two-dimensional arrays cannot. They establish a lower bound of  $\Omega(\sqrt{N})$ , and this model leads to a skew of  $\Theta(N)$  for an H-tree.

Both of these models ignore what we consider to be a fundamental property of skew, namely, its roots in the random variations of propagation time through buffers and wires.

Others [42] have developed equations that relate skew to system performance and stability, in terms of simple timing parameters such as the propagation time and the settling time of the components of the processing elements. The equations specify bounds on the skew for proper operation in

terms of other system timing parameters. No attempt is made to address the nature of the origin of skew, nor to relate its rate of growth with system size.

This chapter presents and analyzes a probabilistic model for the accumulation of skew in a globally distributed signal. We determine upper bounds for the expected clock skew between processing elements in a processor array, and show that under the assumption that the delay is the same at each stage of the clock distribution tree, any array can be clocked with expected skew that is  $O(\log N)$  where N is the number of processing elements.

The organization of the chapter is as follows. In Section 3-2 we present our formal model of global signal distribution and skew accumulation. Section 3-3 presents an analysis of the model and derives upper bounds for the expected skew in a global signal. Section 3-4 applies the results to two examples, and we conclude by comparing our results to previously published results and by discussing the implications of these upper bounds on the construction of large synchronous systems.

#### 3.2. A General Model of Signal Distribution

A global signal, such as a clock, is distributed throughout a processing system by a signal distribution system. The distribution system is composed of a number of buffers (amplifiers) and wires which may be organized in a number of different ways. Two common structures are a bus and a tree.

The clock distribution system can be represented by a graph. It has a single distinguished vertex which is called the *source*. This is where the origin of the global signal is located, and it is the only input to the distribution system. The distribution system can have multiple destinations, but for practical reasons, there is exactly one path from the source to each destination. We assume that a destination is a processing element (PE) which may have its own internal signal distribution system. Using the tools which are developed below, the internal system can be modeled in a similar manner to the global signal distribution system. For our purposes, however, we can think of it as hidden; we concern ourselves only with the global signal system.

There is a second graph superimposed on the clock distribution graph. It is a *communication* graph which specifies the PE-to-PE connectivity. It can take any topology: linear list, mesh, complete, bipartite, etc, and forms connections only among the PEs. The PEs use the global clock to synchronize their communication along the communication graph.

Each buffer and wire in the clock distribution system propagates and delays its incoming signal. Therefore, it is natural to associate every delay element in the signal distribution system, whether a buffer or a wire, with a real random variable,  $d_j$ . The value of the random variable gives the delay contribution of that element. The delay at any stage of the clock distribution system is the sum of the delays from the signal source to that point. An equivalent process takes place in the model. The delay at any point is a real random variable which is the sum of all the random variables along the path from the source to that point.

These definitions constitute the essence of the model. They make it very simple, but extremely general, and allow one to model any clock distribution system. Geometry can be incorporated into the model by attaching an appropriate probability density function to wire delays. There is also the freedom to analyze as much or as little as desired by creating simplified models, in which buffer delays or wire delays can be ignored entirely.

Our primary interest is skew, the distribution of arrival times of a particular clock pulse to all of the PEs that communicate. Since the model is probabilistic, it is not possible to give an expression for the worst-case skew. Rather, we derive an expression for the expected maximum skew by assuming that the PEs are interconnected with a complete graph.

So far, we have made no mention of any particular probability density functions. The total delay through the distribution system, i.e., the arrival time of a clock pulse to a PE, is the sum of a number of random variables. In many cases, it quickly converges to a normal distribution, by the Central Limit Theorem [43-45]. Thus, in the case of the skew computations, the actual distributions attached to buffers and wires are usually relatively unimportant.

The arrival times of a signal to the N PEs constitute a random sample of size N. From this sample, find the difference between the largest of them,  $A_{\rm max}$ , and smallest,  $A_{\rm min}$ . The random variable  $R = A_{\rm max} - A_{\rm min}$  is called the range of the sample. The range is equivalent to the skew in the signal distribution system. The maximum clocking frequency clearly can be no faster than 1/R.

#### 3.3. Analysis and Upper Bounds

The literature contains techniques to compute the expected range of a set of independent identically distributed (iid) random variables. However, little is described about the case when the variables are dependent, as they are in the clock tree. Fortunately, it is possible to use the statistics of iid variates as an upper bound on the statistics of the dependent variates of the clock tree. The relationship is given by Theorem 3-1, which can be paraphrased in the following informal way:

The expected range of a set of random variables, which are dependent because they are the sums of overlapping variables, is no greater than the expected range of the corresponding set of independent random variables.

Let  $y_i$ , i = 1, 2, ..., N be independent identically distributed (iid) real random variables, with N = kn, and let the sets  $\sigma_j$ , j = 1, 2, ..., n be n disjoint subsets of distinct  $y_i$ , each of cardinality k. Let the  $\tau_i$  be similarly defined, with k distinct elements each, except that they are not necessarily pairwise disjoint. Define the corresponding sums of the  $y_i$  by

$$s_j = \sum_{\mathbf{y} \in \sigma_j} \mathbf{y}$$

and

$$t_j = \sum_{\mathbf{y} \in \tau_j} \mathbf{y}$$

We want to show that the expected range of the  $s_j$  dominates the expected range of the  $t_j$ , and so any upper bound for the former also holds for the latter. First we need two lemmas.

**Lemma 3-1.** Let  $F_A(x)$  and  $F_B(x)$  be probability distribution functions for random variables A and B respectively, and suppose further that  $F_A$  and  $F_B$  are differentiable and A and B have finite means and variances. If  $F_A(x) \ge F_B(x)$  for all x, then  $E(A) \le E(B)$ .

**Proof.** Integrating x dF(x) by parts from a to b for  $F_B$  and  $F_A$  and subtracting, we get

$$E(B) - E(A) = \lim_{\substack{a \to -\infty \\ b \to +\infty}} \left[ b\Delta F(b) - a\Delta F(a) - \int_{a}^{b} \Delta F(x) \, dx \right]$$

where  $\Delta F = F_B - F_A \le 0$ . To show that the first two terms go to zero as a and b approach  $-\infty$  and  $+\infty$  respectively, we apply l'Hospital's Rule:

$$\frac{\frac{d}{dq} \left[ \Delta F(q) \right]}{\frac{d}{dq} \left[ \frac{1}{q} \right]} = \frac{\Delta F'(q)}{-\frac{1}{q^2}} = -q^2 \Delta F'(q)$$

$F_A$  and  $F_B$  are differentiable and have finite variances, so the integral

$$\int_{-\infty}^{+\infty} x^2 \, \Delta F'(x) \, dx \tag{3-1}$$

is finite. This implies that the integrand of (3-1) must go to zero as x approaches  $+\infty$  and  $-\infty$ . Therefore

$$E(B) - E(A) = -\int_{-\infty}^{+\infty} \Delta F(x) dx \ge 0$$

The next lemma expresses the intuition that the pre-condition  $y \le \beta$  can only make  $y \le \alpha$  more probable, no matter what  $\alpha$  and  $\beta$  are.

**Lemma 3-2.** For any  $\alpha$  and  $\beta$ , and any continuous probability density P,

$$P(y \le \alpha \mid y \le \beta) \ge P(y \le \alpha)$$

Proof. For convenience write

$$P(y \le \alpha) = G(\alpha)$$

$$P(y \le \alpha \mid y \le \beta) = G(\alpha \mid \beta)$$

$$P(y \le \alpha, y \le \beta) = G(\alpha, \beta)$$

so that we want to show

$$G(\alpha \mid \beta) = \frac{G(\alpha, \beta)}{G(\beta)} \ge G(\alpha)$$

First, consider the case  $\alpha < \beta$ . Since

$$G(\alpha, \beta) = G(\min[\alpha, \beta])$$

we have

$$G(\alpha \mid \beta) = \frac{G(\alpha)}{G(\beta)} \ge G(\alpha)$$

When  $\alpha > \beta$  we have simply

$$G(\alpha \mid \beta) = \frac{G(\beta)}{G(\beta)} = 1 \ge G(\alpha)$$

Lemma 3-2 is easily generalized for any number of conditions to

$$G(\alpha \mid \beta, \gamma, \cdots) \ge G(\alpha)$$

(3-2)

and in fact to the probability distribution of sums of variables, conditioned on other sums, so long as the inequalities in the conditions all go the same way. That is, write any  $\sum y_i \le x$  as  $y_k \le x - \sum_{i \ne k} y_i$  for some k and apply Lemma 3-2. There are no restrictions on  $\alpha$  and  $\beta$ .

**Theorem 3-1.** The expected range of the  $s_i$  is no smaller than the expected range of the  $t_i$ .

**Proof.** Note first that because E[ range ] = E[ max - min ] = E[ max ] - E[ min ], it suffices to show that the expected max of the  $s_j$  cannot be less than the expected max of the  $t_j$ ; the appropriate inequality for the min follows by a symmetric argument.

Let S and T be the maximum of the sums  $s_j$ , j = 1, 2, ..., n and  $t_j$ , j = 1, 2, ..., n respectively, and  $F_S$  and  $F_T$  their distribution functions. By Lemma 3-1, it suffices to show that  $F_T(x) \ge F_S(x)$  for every x.

To simplify notation, let  $S_i$  denote the event  $s_i = \sum_{y \in \sigma_i} y \le x$  and  $T_i$  the event  $t_i = \sum_{y \in \tau_i} y \le x$ . The distribution function  $F_S(x)$  can then be written as

$$F_S(x) = P(S_1, S_2, ..., S_n)$$

=  $P(S_1) P(S_2) \cdots P(S_n)$  because the  $S_i$  are independent.

The distribution of T is

$$F_T(x) = P(T_1, T_2, ..., T_n)$$

$$= P(T_1)P(T_2 \mid T_1)P(T_3 \mid T_1, T_2)P(T_4 \mid T_1, T_2, T_3),...$$

by iterated Bayes' rule. Each factor in this product is

$$P(t_i \le x \mid t_1 \le x, t_2 \le x, \dots, t_{i-1} \le x)$$

All the conditioning is of the form  $\Sigma y \le x$  and so we can apply the generalized version of Lemma 3-2 to show that each factor is  $\ge P(T_i)$ . The result  $F_T \ge F_S$  follows from the fact that the  $s_i$  and  $t_i$  are identically distributed, each being the sum of k iid variables.  $\square$

Now that we have established this theorem, any bound that we show for iid variates is an upper bound for the variates that arise in the clock distribution system model.

At this point we are going to assume that the arrival times are Gaussian, motivated by the Central Limit Theorem. Although no closed-form expression is known for the expected value and the variance of the range of N iid Gaussian distributed random variables, it is possible to obtain asymptotic expressions. We present these as Theorem 3-2, the proof of which is due to Cramér.

**Theorem 3-2.** [45] Let  $x_i$ , i = 1,...,N be random samples from an  $n(\mu,\sigma^2)$  distribution,\* and let  $R = x_{\text{max}} - x_{\text{min}}$  be the difference of the largest and smallest  $x_i$ . Then the expected value of R is asymptotically:

$$E[R] = \sigma \left[ \frac{4\log N - \log\log N - \log 4\pi + 2C}{(2\log N)^{\frac{1}{2}}} + O\left[\frac{1}{\log N}\right] \right]$$

(3-3)

where  $C \approx 0.5772...$  is Euler's constant. The variance of R is given by

$$Var[R] = \frac{\sigma^2}{\log N} \frac{\pi^2}{6} + O\left[\frac{1}{\log^2 N}\right]$$

(3-4)

Equation (3-3) is therefore an asymptotic upper bound on the expected skew in a clock distribution tree with N leaves. Note that  $\sigma$  will in general be a function of N.

We use the notation  $n(\mu, \sigma^2)$  to denote a normal distribution with mean  $\mu$  and variance  $\sigma^2$ .

#### 3.4. Examples

We now analyze two examples of global signal distribution systems. This is meant to clarify how a model is developed for a real problem. The examples represent what we consider to be common, typical clock distribution systems, but they are not intended to represent the full scope of all possibilities.

#### 3.5. Metric-Free Tree

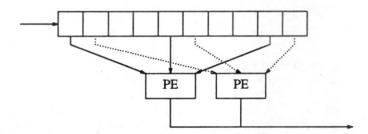

The first example is a *metric-free* tree. This type of topology could be used to implement a large-scale distribution system which would provide a clock to chips on a board or to boards in a system. It does not constrain the circuit to be planar, so it is possible to equalize the lengths of all wires in the tree. Therefore, every wire has the same probability distribution for delay, which can be lumped with the delay of the buffer that follows it. This results in a model of a tree of buffers without wires.

Assume that the global clock signal is distributed via a binary tree of buffers and wires. The root of the tree is the source of the signal, the PEs are placed at the leaves, and the intervening levels consist of buffers and wires. See Figure 3-1 for a schematic representation of the tree.

Figure 3-1: Clock Distribution Tree

In the figure, internal nodes, represented by small circles, are buffers which retransmit the clock signal. The leaf nodes of the tree, represented by squares, are the PEs that perform the actual computation and that communicate among themselves. Lines connecting nodes of the clock tree represent wires that conduct the clock signal to all the PEs.

Let the delay through a buffer of the clock distribution tree be a real random variable,  $d_i$ . The arrival time of a clock signal to any PE is the sum of the delays along the path from the root of the tree

to the PE. Remember that all the delay is caused by the buffers; the effect of a wire is absorbed by the effect of the buffer that follows it. The arrival time at leaf i,  $A_i$ , is therefore the random variable

$$A_i = \sum d_j$$

where the  $d_i$  lie on the path from the root to i.

In order to apply Theorem 3-2, we must estimate the underlying distribution of the  $A_i$ .

Assuming that there are N PEs, each  $A_i$  is the sum of  $\log N d_j$ 's, and that each  $d_j$  has variance  $\sigma_b^2$ . By our Gaussian assumption, the  $A_i$  have the distribution  $n(\mu_b \log N, \sigma_b^2 \log N)$ . Applying Theorem 3-2 with this distribution, we find that the expected skew is

$$E[Skew] = \sigma_b \sqrt{\log N} \left[ \frac{4 \log N - \log \log N - \log 4\pi + 2C}{(2 \log N)^{1/2}} + O\left[\frac{1}{\log N}\right] \right]$$

$$= \sigma_b \frac{4}{\sqrt{2}} \log N + \text{lower order terms}$$

$$= \Theta(\log N)$$

(3-5)

The variance of the skew is

$$Var[skew] = \sigma_b^2 \frac{\pi^2}{6} + O\left[\frac{1}{\log^2 N}\right]$$

which goes to a constant as  $N \to \infty$ .

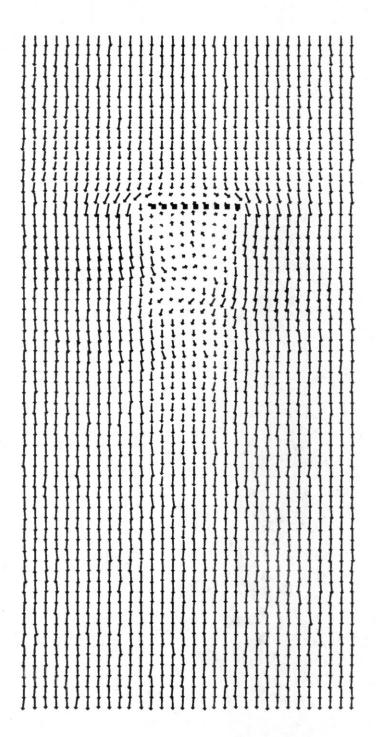

Computer simulations corroborate the asymptotic skew results. Figure 2 shows the asymptotic curve, Equation (3), along with data gathered from simulation of the range of arrival times in a binary clock tree and the range of N iid  $n(0,\log N)$  random variables. Both simulations present the average behavior from 100 trials. The simulations confirm that the range of the iid variates is an upper bound for the range of the dependent variables of the clock distribution tree, as predicted by Theorem 3-1.

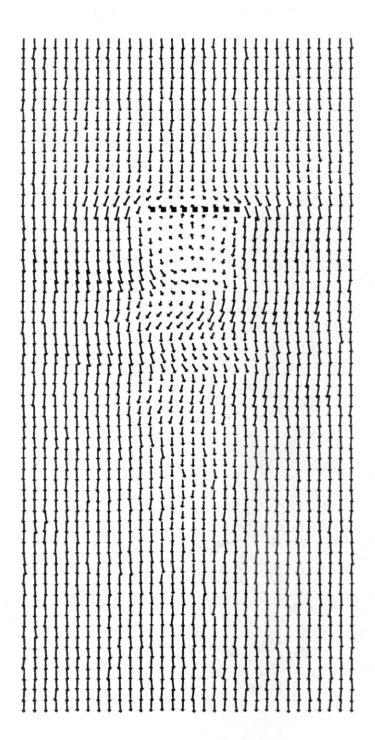

To check the result when the component delays are not Gaussian, we simulated a clock tree where the buffer delays were uniform over [-.5,+.5]. These data were compared to the results from a similar computation when the buffer delay was normally distributed with mean 0 and variance 1/12 (The sum of k uniform [-.5,+.5] variates converges to n(0,k/12)). Figure 3-3 presents the results. Even for trees of small depth, the expected range in both cases is nearly identical. This is due to the rapid convergence of the sums of random variables to a normal distribution.

The explicit inclusion of wire delays into the model does not significantly alter the results. Wires can be considered to contribute an additional random delay at each level of the tree. Assuming that wire delays are distributed similarly to the buffer delays, the effect is to increase the variance of the distribution of arrival times by a constant factor. This does not alter the asymptotic behavior of skew.

Figure 3-2: Range / Skew of Random Variables (Metric Free)

Figure 3-3: Skew in Tree with Uniform and Gaussian Delay

#### 3.6. Metric Tree

The second example is a *metric* tree. This is the type of system that is discussed in [27] and is typical of systems described for VLSI. The central assumption of this topology is that the circuit must be embedded in the plane. If the embedding is to be area-efficient [46], then the wires that connect buffers cannot be the same length everywhere. The delay through a wire therefore depends on the its location in the tree, and cannot be lumped with a buffer delay.

A common tree of this type is the H-tree [47]. We choose to model it here because it is well known, it is feasible to implement in VLSI, and it the focus of the analysis in [27] so we may compare our results with theirs.

There are two distinct views of the effects of increasing system size (number of PEs) under the metric assumption. The first is to assume that a tree with an arbitrary number of leaves can be embedded in the fixed area of the integrated circuit. The alternative to this view sets a lower limit on the size of the smallest feature; in this case the size of a wire at the tree's leaves. Each preceding level is progressively larger and the area of the entire clock tree grows with increasing system size. This view ignores the effect of shrinking feature size but is compatible with increases in chip die size. We will adopt the second model, as did Fisher and Kung.